# **MADE EASY**

India's Best Institute for IES, GATE & PSUs

Test Centres: Delhi, Hyderabad, Bhopal, Jaipur, Pune, Kolkata

# **ESE 2025 : Prelims Exam** CLASSROOM TEST SERIES

# E & T ENGINEERING

Test 4

Section A: Control Systems + Microprocessors and Microcontroller

**Section B**: Network Theory-1 **Section C**: Digital Circuits-1

|     |     |     |     |            | 0   |     |     |     |     |

|-----|-----|-----|-----|------------|-----|-----|-----|-----|-----|

| 1.  | (b) | 16. | (b) | 31.        | (b) | 46. | (a) | 61. | (d) |

| 2.  | (a) |     |     |            |     |     |     |     |     |

|     |     | 17. | (d) | 32.        | (b) | 47. | (a) | 62. | (d) |

| 3.  | (d) | 18. | (a) | 33.        | (d) | 48. | (d) | 63. | (d) |

| 4.  | (d) | 19. | (c) | 34.        | (d) | 49. | (d) | 64. | (b) |

| 5.  | (d) | 20. | (c) | 35.        | (d) | 50. | (b) | 65. | (b) |

| 6.  | (b) | 21. | (b) | 36.        | (b) | 51. | (c) | 66. | (c) |

| 7.  | (d) | 22. | (c) | 37.        | (c) | 52. | (b) | 67. | (b) |

| 8.  | (a) | 23. | (a) | 38.        | (c) | 53. | (c) | 68. | (d) |

| 9.  | (d) | 24. | (c) | 39.        | (c) | 54. | (c) | 69. | (c) |

| 10. | (a) | 25. | (c) | 40.        | (b) | 55. | (a) | 70. | (c) |

| 11. | (d) | 26. | (b) | 41.        | (d) | 56. | (c) | 71. | (d) |

| 12. | (c) | 27. | (d) | 42.        | (a) | 57. | (a) | 72. | (c) |

| 13. | (b) | 28. | (d) | 43.        | (c) | 58. | (c) | 73. | (c) |

| 14. | (c) | 29. | (a) | 44.        | (d) | 59. | (c) | 74. | (d) |

| 15. | (c) | 30. | (d) | <b>45.</b> | (c) | 60. | (a) | 75. | (b) |

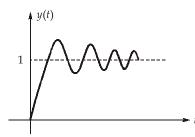

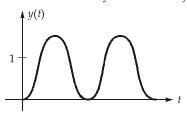

|     |     |     |     |            |     |     |     |     |     |

#### **DETAILED EXPLANATIONS**

#### Section A: Control Systems + Microprocessors and Microcontroller

#### 1. (b)

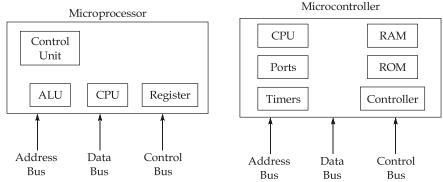

- Micro-controller like micro-processor has Von-Neumann or Hardvard architecture. The

instruction set can be CISC or RISC. However, microcontroller can be a stand alone system

used in embedded system.

- Micro-controller has on-chip memory as well as on chip ports.

Microcontrollers are designed for embedded applications where reliability and fault tolerance

are critical. Since they have an integrated memory, I/O, and processing capabilities, they are

resilient to faults compared to microprocessor-based designs, which rely more on external

components and can be more complex and prone to failure.

#### 2. (a)

- Many programmers prefer assembly level programming over machine language programming because assembly language is simple and easily understandable. It uses easier-to-remember mnemonic codes making it easier to write codes.

- Machine level language is directly understood by the machine. Thus, option (a) is correct.

#### 3. (d)

8085 microprocessor:

- It is manufactured using NMOS technology.

- It is upward compatible with 8080A.

- It is a 40 Pin (dual in line package) chip.

- It is a 8-bit processor.

- It has total 16 address lines with addressing capacity of  $2^{16}$  Bytes = 64 kB.

#### 4. (d)

| $S_1$      | $S_0$ | Microprocessor operation |

|------------|-------|--------------------------|

| 0          | 0     | Halt (no operation)      |

| 0          | 1     | Write operation          |

| 1          | 0     | Read operation           |

| 1 1 Opcode |       | Opcode fetch             |

#### 5. (d)

#### Hardware interrupts:

The 8085 microprocessor has 5 hardware interrupt signals that can be used to interrupt a program execution.

It is also used to accept interrupts from the external devices.

In 8085 microprocessor, TRAP, RST 4.5, RST 5.5, RST 6.5, INTR are the hardware interrupts. Further, There are 8 software interrupts; RST 0-7. Therefore, all the given options are hardware interrupts. Hence, option (d) is correct.

#### 6. (b)

The temporary registers W and Z are used to store data/address temporarily. These are only used by microprocessor to perform internal operations during the programme execution. These registers are also called invisible registers because they are not accessible to user during programme. Therefore, statements 2 and 3 are correct.

#### 7. (d)

As,

Initial address of the memory = 5000 H, and Final address of the memory = 7FFF H size of the memory = (7FFF)H - (5000)H + 1Then,  $= (3000)_{H}$  $(3000)_{H} = (12288)_{10}$

Let 'n' be the number of address lines, then the number of memory locations that can be addressed is given by  $2^n$ . Thus,

$$2^n \ge 12288$$

$$n = 14$$

Minimum of 14 address lines are required.

Therefore, number of address lines is 14.

As in the memory location 5000H, eight bit of data (0110 1010) is present. Thus, number of data lines required is 8.

#### 8. (a)

For I/O mapped I/O interfacing, the number of T-states needed is 10 T-states whereas for memorymapped I/O, 13, T-states (STA, LDA) or 7 T-states (MOV M, R) is needed.

#### 9. (d)

We know that, XRA A is the instruction through which we clear the accumulator.

XRA A;  $[A] \leftarrow 00 H$ MOV L, A;  $[L]\leftarrow 00 H$ MOV H, L;  $[H] \leftarrow 00 H$ INX H;  $[HL] \leftarrow [HL] + 0001 H$  $[HL] \leftarrow [HL] + [HL] = 0001 H + 0001 H = 0002 H$ DAD H;

Content of HL pair after execution of the program = 0002 H

#### 10. (a)

All the statements are correct.

#### 11. (d)

- The 8086 microprocessor has two functional units: Execution unit (EU) and Bus interface unit (BIU).

- The BIU interface the 8086 to the outside world. It fetches, reads data from memory and ports, and writes data to memory and I/O ports.

- EU receives program instruction codes and data from the BIU, executes these instructions.

- EU and BIU function independently, whenever the execution unit starts decoding and executing fetched instructions, the BIU fetches additional instructions to the queue from the code memory for execution.

Thus, all the statements are correct.

#### 12. (c)

$TF \rightarrow In 8086$ , if TRAP flag is set then microprocessor can be used in single step mode for debugging.

#### 13. (b)

In 8086 microprocessor, TYPE 2 interrupt represents non-maskable interrupt (NMI). The interrupt vector address of the interrupt is found by multiplying the type by 4. Thus, for NMI, interrupt vector address is  $2 \times 4 = 8_{10} = 00008 \text{ H}$

#### 14. (c)

Addressing Modes of 8086:

- 1. Immediate Addressing Mode: The operand is specified in the instruction itself.

- $\Rightarrow$  MOV BX, 3598 H

- 2. Direct Addressing Mode: The effective address of the operand is written directly in the instruction.

- $\Rightarrow$  ADD BL, [0103]

- 3. Register Addressing Mode: The operand is stored in the register.

- $\Rightarrow$  MOV AX, CX

- 4. Register Indirect Addressing Mode: The operand's offset in the segment is stored in the register.

- $\Rightarrow$  MOV BX, [BP]

- 5. Register Relative Addressing Mode: The operand's offset in the segment is obtained by adding an 8-bit or 16-bit displacement to the contents stored in any one of the registers BX, BP, SI and DI.

- $\Rightarrow$  MOV CL, [BX + 05 H]

- 6. Indexed Addressing Mode: The operand's offset in the segment is the sum of the content of an index register SI or DI and an 8 bit or 16 bit displacement.

- $\Rightarrow$  MOV BX, [SI + 1528 H]

- 7. Based Index Addressing Mode: The operand's offset in the segment is sum of the content of a base register BX and an index register SI or DI.

- $\Rightarrow$  ADD CX, [BX + SI]

- 8. Relative Based Indexed Addressing Mode: The operand's offset in the segment is sum of the content of a base register BX, an index register SI or DI and an 8 bit or 16 bit displacement.

⇒ MOV AX, [BX + SI + 1234 H]

- 15. (c)

In the HL register pair, 'H' is the higher order register containing the higher order byte "15 H" and 'L' is the lower order register containing the lower order byte "EF H".

i.e.,

$$[H] \leftarrow 15 \text{ H}$$

and  $[L] \leftarrow \text{EF H}$

When INR H is executed, it increments the content of H register by 01 H i.e.

$$[H] \leftarrow 15 + 01$$

i.e.,  $[H] \leftarrow 16 H$  and  $[L] \leftarrow EF H$

$$\therefore$$

Content of HL pair =  $(16EF)_{H}$

Therefore, option (c) is correct.

16. (b)

We know that,

open loop transfer function for standard second order system is given as

$$G(s)H(s) = \frac{\omega_n^2}{s(s+2\xi\omega_n)}$$

Now,

Velocity error coefficient,  $k_v = \lim_{s \to 0} sG(s)H(s)$

$$= \lim_{s \to 0} s \frac{\omega_n^2}{s(s + 2\xi\omega_n)} = \frac{\omega_n}{2\xi}$$

$$e_{ss} = \frac{1}{k_V} = \frac{2\xi}{\omega_n}$$

- 17. (d)

- ORA R (OR register with accumulator)  $\Rightarrow$  All flags are affected and CY = 0, AC = 0.

- XRA M (EXOR memory with accumulator) ⇒ All flags are affected and AC = 0, CY = 0.

- ANA M (AND memory with accumulator)  $\Rightarrow$  All flags are affected and AC = 1, CY = 0.

- 18. (a)

We know that,

At 3 dB frequency,  $|G(j\omega)| = \frac{1}{\sqrt{2}}$  times of maximum magnitude. (valid for both closed loop and open loop stable system)

Case-I: For open loop system,

$$|G(j\omega)| = \left|\frac{k}{(j\omega + A)}\right| = \frac{k}{\sqrt{\omega^2 + A^2}}$$

$$|G(j\omega)|_{\text{max}}$$

occurs at  $\omega = 0$  i.e.,  $|G(j\omega)|_{\text{max}} = \frac{k}{A}$

Now, from above mentioned definition, at 3 dB frequency,

$$\frac{k}{\sqrt{A^2 + \omega^2}} = \frac{k}{A} \times \frac{1}{\sqrt{2}}$$

$$A^2 + \omega^2 = 2A^2$$

As  $\omega = 1 \text{ rad/sec}$ ,

$$A^{2} + 1 = 2A^{2}$$

$$A^{2} = 1$$

$$A = \pm 1$$

(A = -1 is discarded; because for A = -1, system become unstable)

Hence, we get A = 1

Case-II: For closed loop system,

For unity feedback closed loop system, transfer function becomes

T.F =

$$\frac{k}{s+A+k}$$

$|G(j\omega)| = \frac{k}{\sqrt{\omega^2 + (k+A)^2}}$

or

$$|G(j\omega)|_{\text{max}}$$

at  $\omega = 0$  i.e.,  $|G(j\omega)|_{\text{max}} = \frac{k}{\sqrt{(k+A)^2}} = \frac{k}{(k+A)}$

Now, using the above mentioned definition, at 3 dB frequency,

$$\frac{k}{\sqrt{\omega^2 + (k+A)^2}} = \frac{k}{(k+A)} \times \frac{1}{\sqrt{2}}$$

$$\sqrt{2}(k+A) = \sqrt{\omega^2 + (k+A)^2}$$

On squaring both sides,

$$2(k + A)^2 = \omega^2 + (k + A)^2$$

As 3 dB frequency,  $\omega = 2 \text{ rad/sec}$  and A = 1,

$$2(k + 1)^{2} = (2)^{2} + (k + 1)^{2}$$

$$(k + 1)^{2} = 4$$

$$k + 1 = \pm 2$$

$$k = \pm 2 - 1$$

$$k = 1 \text{ or } -3$$

For k = -3, the system becomes unstable. Hence, k = -3 is discarded.

Thus, k = 1 and A = 1.

#### 19. (c)

From the given block diagram,

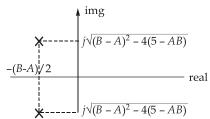

$$\frac{C(s)}{R(s)} = \frac{5}{(s-A)(s+B)+5} = \frac{5}{s^2 + s(B-A) + (5-AB)} \qquad \dots (i)$$

Now, from the characteristic equation, we get poles of the system as

$$s_{1,2} = \frac{-(B-A) \pm \sqrt{(B-A)^2 - 4(5-AB)}}{2}$$

MADE EASY

Now,

real part of poles,  $s_{1, 2} = \frac{-(B-A)}{2} = \frac{-1}{2}$

It is given that poles are symmetric about s = -1/2, thus,

$$\frac{-(B-A)}{2} = -\frac{1}{2}$$

...(ii)

Also, we have open loop transfer function as  $\frac{5}{(s-A)(s+B)}$ . Thus, open loop DC gain of the system

is obtained by putting s = 0 as  $\frac{-5}{AB}$ . It is given that,  $\frac{-5}{AB} = -\frac{5}{2}$

Hence,

$$AB = 2$$

...(iii)

Now from equation (ii) and (iii) we get A = 1 and B = 2.

Thus, characteristic equation of the system is  $s^2 + s(B - A) + 5 - AB = 0$  i.e.  $s^2 + s + 3 = 0$ . Therefore, option (c) is correct.

20.

PI controller is used to overcome the problem of steady state error. Therefore, option (c) is correct.

21. (b)

We know that,

|sI - A| gives the characteristic equation of the system. Therefore, option (b) is correct.

22. (c)

Nyquist plot intersects unit circle at (-1, j0), which gives the gain cross-over frequency

Phase Margin, PM =

$$\angle G(j\omega)H(j\omega)\big|_{\omega=\omega_{gc}} + 180^{\circ}$$

where.

$\omega_{gc}$  = gain crossover frequency

Here, at gain crossover frequency  $(\omega_{gc})$ , phase angle of open loop transfer function is -180°. Thus,

$$PM = -180^{\circ} + 180^{\circ}$$

$$PM = 0 degree$$

23. (a)

We know that, for an LTI system,

$$x(t) = A \cos(\omega_0 t + \phi_1)$$

$$G(j\omega)$$

$$y(t) = B \cos(\omega_0 t + \phi_2)$$

$$x(t) = A \cos(\omega_0 t + \phi_1)$$

$$B = A |G(j\omega)|_{\omega = \omega_0}$$

$$\phi_2 = \phi_1 + \angle G(j\omega)|_{\omega = \omega_0}$$

then,

Now, on comparison, we get

$$B = 1; A = \frac{\sqrt{3}}{2}$$

We have,

$$|G(j\omega)| = \frac{B}{A}$$

$|G(j\omega)|_{\text{at }\omega = 2 \text{ rad/sec}} = \frac{2}{\sqrt{3}}$

As

$$\phi_2 = -\frac{\pi}{3}$$

and  $\phi_1 = -\frac{\pi}{2}$  then,  $\angle G(j\omega)_{\omega = 2 \text{ rad/sec}} = \phi_2 - \phi_1$

$$= -\frac{\pi}{3} - \left(-\frac{\pi}{2}\right) = \frac{\pi}{6}$$

Since the system has one pole and one zero, let the Transfer function of the system be

$$G(s) = \frac{Ks}{(s+A)}$$

$$G(j\omega) = \frac{j\omega K}{(j\omega+A)}$$

$$|G(j\omega)|_{\omega = 2 \text{ rad/sec}} = \left|\frac{2jK}{(j2+A)}\right| = \frac{2K}{\sqrt{A^2+4}} = \frac{2}{\sqrt{3}} \qquad \dots(i)$$

$$\angle G(j\omega)|_{\omega = 2} = \frac{\pi}{2} - \tan^{-1}\frac{\omega}{A} = \frac{\pi}{6}$$

$$\frac{\pi}{2} - \frac{\pi}{6} = \tan^{-1}\left(\frac{2}{A}\right)$$

$$\tan\frac{\pi}{3} = \frac{2}{A}$$

$$A = \frac{2}{\sqrt{3}}$$

Now, substituting  $A = \frac{2}{\sqrt{3}}$  in equation (i), we get

$$\frac{2K}{\sqrt{\frac{4}{3}+4}} = \frac{2}{\sqrt{3}}$$

$$2\sqrt{3}K = 2\sqrt{\frac{16}{3}}$$

$$2\sqrt{3}K = \frac{2\times 4}{\sqrt{3}}$$

$$\frac{2\times\sqrt{3}\times\sqrt{3}}{8} = \frac{1}{K}$$

$$K = \frac{4}{3}$$

Therefore,

$$T(s) = \frac{\frac{4}{3}s}{s + \frac{2}{\sqrt{3}}}$$

24. (c)

> Initial slope of -40 dB/dec implies double poles at origin, thus the transfer function has the term

$$\frac{K}{s^2} = \frac{K}{(j\omega)^2} \qquad \dots (i)$$

The initial slope of the line intersects the  $\omega$  axis at  $\omega$  = 8 rad/sec. Thus,

$$|H(j\omega)| = 20 \log K - 20 \log \omega^2 = 0$$

... at  $\omega = 8 \text{ rad/sec}$

$20 \log K = 20 \log (8)^2$  ...(ii)

At  $\omega$  = 3 rad/sec, slope changes to -20 dB/dec, it shows the presence of zero at  $\omega$  = 3.

Thus, the term

$$\left(1+\frac{s}{3}\right)$$

...(iii)

At  $\omega$  = 15 rad/sec, slopes changes to -18 dB/oct

-20 dB/dec = -6 dB/octWe know that,

$$-18 \text{ dB/oct} = -60 \text{ dB/dec}$$

Thus, the slope changes by (-60 + 20) = -40 dB/dec indicating, presence of two poles at  $\omega = 15$ ,

thus the term

$$\frac{1}{\left(1+\frac{s}{15}\right)^2}$$

...(iv)

Now, on combining (i), (ii), (iii) and (iv), we get

$$T(s) = 64 \frac{\left(\frac{s}{3} + 1\right)}{\left(\frac{s}{15} + 1\right)^2 s^2}$$

25. (c)

We have closed loop transfer function as,

$$T(s) = \frac{a_{n-1}s + a_n}{s^n + a_1s^{n-1} + \dots + a_{n-1}s + a_n}$$

As the system has unity feedback, then open loop transfer function is given as

$$G(s)H(s) = \frac{a_{n-1}s + a_n}{s^n + a_1s^{n-1} + \dots + (a_{n-1}s + a_n) - (a_{n-1}s + a_n)}$$

$$G(s)H(s) = \frac{a_{n-1}s + a_n}{s^n + a_1s^{n+1} + \dots + a_{n-2}s^2}$$

Now, error coefficients,

$$\begin{split} k_p &= \lim_{s \to 0} G(s) H(s) \; ; k_v = \lim_{s \to 0} s G(s) H(s) \\ k_p &= \lim_{s \to 0} \frac{(a_{n-1}s + a_n)}{s^2 (s^{n-2} + a_1 s^{n-3} \dots + a_{n-2})} = \infty \; ; \\ k_v &= \lim_{s \to 0} \frac{s (a_{n-1}s + a_n)}{s^2 (s^{n-2} + a_1 s^{n-3} \dots + a_{n-2})} = \infty \; ; \\ k_a &= \lim_{s \to 0} s^2 G(s) H(s) = \lim_{s \to 0} \frac{s^2 (a_{n-1} + a_n)}{s^2 (s^{n-2} + a_1 s^{n-3} + \dots + a_{n-2})} \\ k_a &= \left(\frac{a_n}{a_{n-2}}\right) \end{split}$$

Now, steady state error for

Step input =

$$\frac{A}{k_p} = \frac{A}{\infty} = 0$$

ramp input =  $\frac{A}{k_v} = \frac{A}{\infty} = 0$

parabolic input =  $\frac{A}{k_a} = \frac{A}{\left(\frac{a_n}{a_{n-2}}\right)} = \frac{A(a_{n-2})}{a_n}$

26. (b)

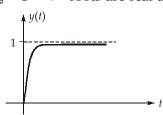

• For critically damped system,  $\xi = 1 \implies$  roots are real and equal

• For over damped system,  $\xi > 1 \implies$  roots are real and unequal

• For underdamped system,  $\xi < 1 \implies$  roots are complex conjugate

• For undamped system,  $\xi = 0 \implies$  roots are symmetric to  $j\omega$ -axis

27. (d)

All the statments are correct.

- **28. (d)** Phase margin is calculated at gain crossover frequency. Thus, statement 2 is not correct.

- 29. (a)

We know that,

$$\angle G(j\omega)H(j\omega) = -\tan^{-1}\left(\frac{\omega A}{2}\right) - \tan^{-1}\left(\frac{\omega A}{1}\right) - \tan^{-1}\left(\frac{3\omega A}{1}\right)$$

At  $\omega = \omega_{pc'}$

$$\angle G(j\omega)H(j\omega)|_{\omega = \omega_{pc}} = -180^{\circ}$$

$$-\tan^{-1}\left(\frac{\omega_{pc}A}{2}\right) - \tan^{-1}(\omega_{pc}A) - \tan^{-1}(3\omega_{pc}A) = -180^{\circ}$$

As,  $\omega_{pc}$  = 1 rad/sec, then

$$\tan^{-1}\left(\frac{A}{2}\right) + \tan^{-1}(A) + \tan^{-1}(3A) = 180^{\circ}$$

$$\tan^{-1}\left(\frac{A}{2}\right) + \tan^{-1}\left(\frac{4A}{1 - 3A^{2}}\right) = 180^{\circ}$$

$$\left(\begin{array}{c} 2 \end{array}\right) \qquad \left(\begin{array}{c} 1 - 3A^2 \end{array}\right) = 100$$

$$\left(\begin{array}{c} \frac{A}{2} + \frac{4A}{1 - 2A^2} \end{array}\right)$$

$$\tan^{-1}\left(\frac{\frac{A}{2} + \frac{4A}{1 - 3A^2}}{1 - \frac{2A^2}{1 - 3A^2}}\right) = 180^{\circ}$$

$$\frac{\frac{A}{2} + \frac{4A}{1 - 3A^2}}{1 - \frac{2A^2}{1 - 3A^2}} = 0$$

$$\frac{A}{2} + \frac{4A}{1 - 3A^2} = 0$$

$$A(1 - 3A^2) + 8A = 0$$

$$A - 3A^3 + 8A = 0$$

$$9A = 3A^3$$

$$3A^2 = 9$$

$$A^2 = 3$$

$$A = \sqrt{3}; -\sqrt{3}$$

$A=-\sqrt{3}$  is discarded as for  $A=-\sqrt{3}$ , the system become unstable. Thus,  $A=\sqrt{3}$ .

30. (d)

#### 31. (b)

• Gain Margin 0 dB, it implies

$$-20 \log a = 0$$

$$a = 1$$

For a < 1, system is stable

a > 1, system is unstable

a = 1, system is marginally stable

Thus, statement (i) is correct.

• Phase margin is determined at gain cross over frequency  $\omega_{gc'}$  which depends on system gain. The gain cross-over frequency is determined by

$$\left|G(j\omega)H(j\omega)\right|_{\omega=\omega_{gc}} = 1$$

Phase angle at  $\omega = \omega_{gc}$  is  $\angle G(j\omega_{gc})H(j\omega_{gc})$ , thus we have

$$PM = \angle G(j\omega_{gc})H(j\omega_{gc}) + 180^{\circ}$$

Thus, statement (ii) is incorrect.

32. (b)

The characteristic equation of the system is  $P(s) = s^4 + 8s^3 + 24s^2 + 32s + k$ Now, forming Routh-Hurtwitz table,

$$s^4$$

$$s^3$$

$$s^2 \quad \frac{24 \times 8 - 32}{8} = 20 \quad k$$

$$c^{1}$$

$$32 - \frac{8k}{20}$$

$$s^0$$

Now, for stable system

$$k > 0$$

...(i)

and

$$32 - \frac{8k}{20} > 0$$

$$32 \times 20 - 8k > 0$$

$$\frac{32 \times 20}{8} > k$$

Thus, for stable system, *k* must be less than 80.

#### 33. (d)

We know that, in a root locus plot,

centroid lies on real axis only i.e., imaginary axis coordinate is zero. And the real axis coordinate is given as

$$\sigma = \frac{\Sigma \text{ real part of all the poles} - \Sigma \text{ real part of all the zeros}}{(\text{number of poles}) - (\text{number of zeros})}$$

Now,

$$\text{zeros} = -A; \text{ Number of zeros, } Z = 1$$

$$\text{Poles} = 0, -B, -1 \text{ and } -1; \text{ Number of poles, } P = 4$$

$$\text{centroid} = \frac{(0 - B - 1 - 1) - (-A)}{4 - 1} = -5$$

$$-B - 2 + A = -15$$

$$A - B = -13$$

Therefore, option (d) is correct.

# 34. (d)

- The instrument used for plotting the root locus is called spirule.

- The root locus must be symmetrical with respect to the real axis of the s-plane because complex roots appear as complex conjugate pairs.

- The root locus shows the locus of the poles of the closed loop system with variation of open loop gain k. Thus, it could be used to determine the range of k for which the system is stable i.e. the roots lie on the left side of the  $j\omega$  axis.

Thus, all the given statements are correct.

#### 35. (d)

In an 8085 microprocessor, PUSH operations requires more clock cycles than POP operation. In a PUSH operation, the stack pointer needs to be pre-decremented before writing registers, whereas a POP operation uses the address already in the stack pointer. PUSH instruction takes 1 T-state (6 clock cycles) for fetch and decoding operation and 2 T-states (6 clock cycles) for write operation; whereas POP instruction takes 4 clock cycles for fetch and decoding operation and 2 T-states (6 clock cycles) for read operation. Hence, Statement (I) is false and Statement (II) is correct.

#### 36. (b)

The 8085 microprocessor uses multiplexed address/data lines (AD7-AD0). The ALE (Address Latch Enable) is a signal used to demultiplex the address and data lines, using an external latch. ALE is a positive going pulse generated when a new operation is started by microprocessor. When the pulse goes high i.e. ALE = 1, it makes address bus enable and when ALE = 0, it makes data bus enable. Both Statement (I) and Statement (II) are true but Statement (II) is not the correct explanation of Statement (I).

### 37. (c)

Phase margin gives the better estimate of damping ratio than the gain margin. Hence, Statement (II) is not correct.

38. (c)

Statement (I) is correct as a stable system might become unstable on giving negative feedback to it. And, a system's gain always decreases on giving feedback (negative) to it. Therefore, Statement-(II) is incorrect.

# **Section B: Network Theory-1**

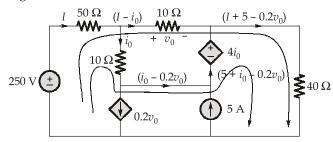

39. (c)

Let  $V_1$  be the node voltage.

Applying KVL around the outer loop,

$$-250 + 50I + 10(I - i_0) + 40(I + 5 - 0.2v_0) = 0$$

$$100I - 10i_0 - 8v_0 = 50$$

$$100I - 10i_0 - 80 (I - i_0) = 50$$

[Here,  $v_0 = 10(I - i_0)$ ]

...(i)

$\Rightarrow$

On applying KVL,

$$-250 + 50I + 10i_0 - 4i_0 + 40(I + 5 - 0.2v_0) = 0$$

$$90I + 6i_0 + 200 - 8v_0 = 250$$

$$90I + 6i_0 + 200 - 80(I - i_0) = 250$$

$$I + 8.6i_0 = 5$$

$$\Rightarrow I = 5 - 8.6i_0$$

Using equation (i),

$$2(5 - 8.6i_0) + 7i_0 = 5$$

$i_0 = 0.49 \text{ A}$

$2I + 7i_0 = 5$

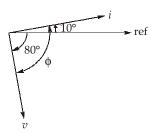

40. (b)

Given,

$\Longrightarrow$

$$v = 100 \cos(100t - 80^{\circ})V$$

$i = 10 \cos(100t + 10^{\circ})A$

The vector diagram is

As  $\phi = 90^{\circ}$  and *i* leads *V*, it implies that the element is capacitor.

Test 4

$$X_C = \frac{V_m}{I_m} = \frac{100}{10} = 10 \Omega$$

$$C = \frac{1}{\omega X_C} = \frac{1}{100 \times 10} = 1 \times 10^{-3} = 1 \text{ mF}$$

41. (d)

.:.

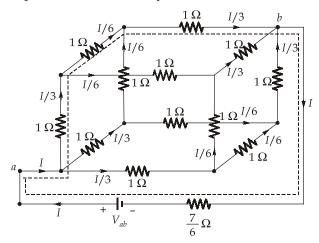

Since the path resistance between a and b are equal in all the paths, we can apply current division rule and then obtain the equivalent resistance by ohm's law.

Apply KVL in the shown path,

$$\begin{split} -V_{ab} + \left(\frac{I}{3} \times 1\right) + \left(\frac{I}{6} \times 1\right) + \left(\frac{I}{3} \times 1\right) + \left(\frac{7}{6} \times I\right) &= 0 \\ V_{ab} = \left(\frac{5}{6} + \frac{7}{6}\right)I = \frac{12}{6}I = 2I \\ \Rightarrow V_{ab} &= 2I \end{split}$$

42. (a)

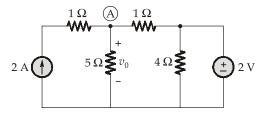

> At steady state, the inductances would behave as short circuit against d.c. excitation at  $t = \infty$ . Similarly, capacitor would act as open circuit against d.c. excitation at  $t = \infty$ . At steady state, the equivalent circuit can be obtained as below:

Apply KCL at node (A),

$$-2 + \frac{v_0}{5} + \frac{v_0 - 2}{1} = 0$$

$$v_0 \left(\frac{1}{5} + 1\right) = 2 + 2$$

$$v_0\left(\frac{6}{5}\right) = 4$$

$$v_0 = \frac{20}{6} = \frac{10}{3} = 3.333 \text{ V}$$

43. (c)

$\Rightarrow$

The input impedance of the given circuit is given by

$$Z_{\text{in}} = 3 + [1 \parallel j2] = 3 + \frac{(1 \times j2)}{(1+j2)} = 3 + \frac{j2(1-j2)}{5} = 3 + j0.4 + 0.8$$

$Z_{\text{in}} = 3.8 + j0.4 \Omega$

The input current will be in phase with the supply voltage provided the reactive part of the impedance does not exist after inserting the capacitor in series.

$$\Rightarrow \frac{j}{\omega C} = j0.4$$

$$\Rightarrow C = \frac{1}{\omega \times 0.4} = \frac{1}{100 \times 0.4} = 0.025$$

$$\Rightarrow C = 25 \text{ mF}$$

44. (d)

$$Y_R = \frac{1}{R} \angle 0^\circ = (0.5 + j0) \text{ mho}$$

$$Y_C = \frac{1}{X_C} \angle 90^\circ = \frac{1}{1.25} \angle 90^\circ = 0.8 \angle 90^\circ = j0.8 \text{ mho}$$

Net admittance,  $Y = Y_R + Y_C$

$$= (0.5 + j0.8) \text{ mho}$$

$$I = EY = 5 \angle 0^\circ \times (0.5 + j0.8)$$

$$= (2.5 + j4)A$$

45. (c)

.:.

The input impedance is,

$$Z_{in} = 5 + \left[ -j4 \parallel (2+j2) \right]$$

$$= 5 + \frac{-j4(2+j2)}{-j4+2+j2}$$

$$= 5 + \frac{8-8j}{2-2j}$$

$$= 5 + \frac{(8-8j)(2+2j)}{8}$$

$$= 5 + \frac{16+16j-16j+16}{8}$$

$$Z_{in} = 9 \Omega$$

As the input impedance is purely resistive, the p.f. would be unity.

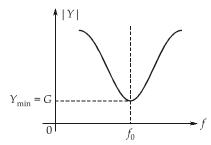

- 46. (a)

- The admittance of a parallel RLC circuit is given as  $Y = G + j(B_C B_L)$ . At resonance,  $B_C = B_{L'}$ thus the net susceptance is zero and the the net admittance is minimum;  $Y_{\min} = G$ .

Since net admittance is minimum, the net impedance is maximum and purely resistive. Thus, the current is minimum and in phase with the applied voltage.

Hence, statements 1, 2 and 3 are correct.

47.

At resonance, imaginary part of input impedance must be zero.

We have,

$$Z_{\text{in}} = \frac{-j}{2\omega} + \left[j\omega \| 1\right] = \frac{-j}{2\omega} + \frac{j\omega}{1+j\omega}$$

$$= \frac{-j}{2\omega} + \frac{j\omega(1-j\omega)}{1+\omega^2}$$

$$= \frac{-j}{2\omega} + \frac{j\omega}{1+\omega^2} + \frac{\omega^2}{1+\omega^2}$$

At resonance,

$$\frac{-1}{2\omega} + \frac{\omega}{1 + \omega^2} = 0$$

$$\frac{\omega}{1 + \omega^2} = \frac{1}{2\omega}$$

$$2\omega^2 = 1 + \omega^2$$

$$\omega = 1 \text{ rad/sec}$$

- 48. (d)

- $Q = \frac{X_L}{R} = \frac{\omega L}{R}$ For series RL circuit,

- $Q = \frac{X_C}{R} = \frac{1}{\omega RC}$ For series RC circuit,

- $Q = \frac{R}{X_I} = \frac{R}{\omega L}$ For parallel RL circuit,

- $Q = \frac{R}{X_c} = \omega RC$ For parallel RC circuit,

...(i)

# 49. (d)

Given,

$$v_L = 300 \sin(1000t) \text{ V}$$

$$R = 20 \Omega$$

$$\phi = 45^{\circ}$$

$$V_{L(\text{max})} = 2V_{C(\text{max})}$$

$$\sqrt{2}V_L = 2\sqrt{2}V_C$$

$$I \times X_L = 2I \times X_C$$

We have,

$$\cos \phi = \frac{R}{Z}$$

$\Rightarrow$

$$\cos 45^{\circ} = \frac{20}{Z}$$

$\Rightarrow$

$$Z = 20\sqrt{2} \Omega$$

For series R-L-C circuit,

$$Z = \sqrt{R^2 + (X_L - X_C)^2}$$

Using equation (i),

$$20\sqrt{2} = \sqrt{(20)^2 + (2X_C - X_C)^2}$$

$$800 = 400 + X_C^2$$

$$X_C^2 = 400$$

$$X_C = 20 \Omega$$

# 50. (b)

$\Longrightarrow$

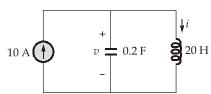

For t < 0, 10 u(t) = 0. At  $t = 0^-$ , since the circuit is source-free, the capacitor is uncharged.

$$v(0^{-}) = 0 \text{ V}$$

$$i(0^{-}) = 0 \text{ A}$$

For t > 0, 10u(t) = 10, so the equivalent circuit is,

Since the inductor current and capacitor voltage cannot change abruptly,

$$i(0^+) = i(0^-) = 0$$

A

$$v(0^+) = v(0^-) = 0 \text{ V}$$

$$v(0) = \frac{Ldi(0)}{dt}$$

$$\Rightarrow \frac{di(0)}{dt} = \frac{v(0)}{I} = 0 \text{ A/s}$$

Test 4

The s-domain equivalent of the above circuit is,

Applying KCL at node a,

$$\frac{-10}{s} + \frac{V(s)}{\left(\frac{5}{s}\right)} + \frac{V(s)}{20s} = 0$$

$$V(s)\left[\frac{s}{5} + \frac{1}{20s}\right] = \frac{10}{s}$$

$$\Rightarrow V(s) \times \left\lceil \frac{4s^2 + 1}{20} \right\rceil = 10$$

$$V(s) = \left[ \frac{50}{s^2 + \left(\frac{1}{2}\right)^2} \right]$$

Taking inverse Laplace transform on both sides,

$$v(t) = \frac{50}{\left(\frac{1}{2}\right)} \times \sin\left(\frac{1}{2}t\right) = 100\sin(0.5t) \text{ V}$$

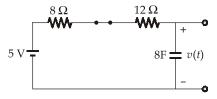

#### 51. (c)

At  $t = 100^-$ , it is given that  $v(100^-) = -3 \text{ V}$ .

Since the voltage across the capacitor cannot change instantaneously,  $v(100^-) = v(100^+) = -3 \text{ V}$ . The switching takes place at time t = 100.

For *t* ≥ 100:

The voltage across the capacitor is,

$$v(t) = v(\infty) + [v(100) - v(\infty)]e^{-(t - 100)/\tau} \qquad \dots (i)$$

After a long time, the circuit reaches steady state and capacitor acts like an open circuit.

$$\therefore \qquad v(\infty) = 5 \text{ V}$$

The thevenin resistance across the capacitor terminals is,

$$R_{\rm Th} = 8 + 12 = 20 \ \Omega$$

and the time constant is,

$$\tau = R_{\text{Th}}C = 20 \times 8 = 160 \text{ sec}$$

Thus, from equation (i),

$$v(t) = 5 + [-3 - 5]e^{-(t - 100)/160}$$

$$v(t) = 5 - 8e^{-(t - 100)/160} V$$

At t = 200 seconds,

$$v(200) = 5 - 8e^{-(200 - 100)/160} = (5 - 8e^{-5/8}) \text{ V}$$

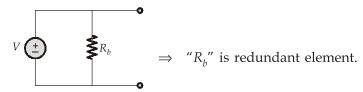

#### 52. (b)

Any resistance in series with current source is redundant.

$$R_a$$

$\Rightarrow$  " $R_a$ " is redundant element.

Any resistance in parallel with voltage source is redundant.

#### 53. (c)

From circuit P; we get

$$\frac{E}{R} = 0.5 \text{ A} \implies E = 0.5R \qquad \dots (i)$$

From circuit Q, we get

$$\frac{E}{R_1} = 0.4 \text{ A} \implies E = 0.4R_1$$

*:*.

$$R_1 = R + R' \text{ i.e., } E = 0.4(R + 5)$$

$E = 0.4R + 2$  ...(ii)

From circuit *R*, we get,

$$\frac{E}{R_2} = 0.2 \quad \Rightarrow \quad E = 0.2R_2$$

.:.

$$R_2 = R_1 + R'' = R + 5 + R''$$

$E = 0.2(R + 5 + R'') = 0.2R + 1 + 0.2R''$  ...(iii)

From equation (i) and (ii), we get

$$0.5R = 0.4R + 2$$

$$0.1R = 2$$

$$R = 20 \Omega$$

...(iv)

On substituting  $R = 20 \Omega$  in equation (i) we get E = 10 volt.

Using (iv), and (v) in equation (iii), we get

$$10 = (0.2 \times 20) + 1 + 0.2R''$$

$$10 = 4 + 1 + 0.2R''$$

$$10 = 4 + 1 + 0.2R''$$

$$\frac{5}{0.2} = R''$$

$$R'' = 25 \Omega \qquad \dots (vi)$$

Now, in circuit 'Q' is  $E \times I = 10 \times 0.4 = 4$  Watt

Therefore, *Q* is matched to 1.

...(v)

Now, in circuit 'P' value of  $R_{\rm th}$  = 20  $\Omega$  and in circuit 'R', total extra resistance added is ' $(R_2 - R)$ ' i.e.,

$$\left(50 - \frac{10}{0.5}\right)\Omega = 30 \ \Omega$$

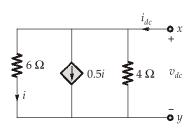

### 54. (c)

The current,

$$i_{dc} = \frac{v_{dc}}{4} + 0.5i + i$$

$$i_{dc} = 0.25 v_{dc} + 1.5i \qquad ...(i)$$

$$i = \frac{v_{dc}}{6}$$

But

$$\begin{split} i_{dc} &= 0.25 v_{dc} + 1.5 \bigg(\frac{v_{dc}}{6}\bigg) \\ i_{dc} &= 0.25 v_{dc} + 0.25 v_{dc} \\ i_{dc} &= 0.5 v_{dc} \end{split}$$

$\Rightarrow$

$$R_{\rm Th} = \frac{v_{dc}}{i_{dc}} = \frac{1}{0.5} = 2 \ \Omega$$

# 55. (a)

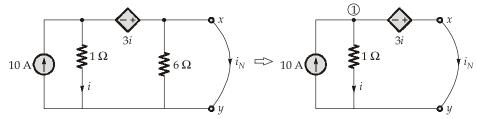

### 56. (c)

To determine Norton's equivalent current source, we consider short circuit across x-y terminal as shown in figure.

Apply KCL at node (1),

$$-10 + i + i_N = 0$$

...(i)

Apply KVL at node (1),

$$-i - 3i = 0$$

$$i = 0$$

$$-10 + 0 + i_N = 0$$

$$i_N = 10 \text{ A}$$

57. (a)

$\Longrightarrow$

The power supply which is actually consumed in an AC circuit is called Active Power.

From equation (i),

# Section C : Digital Circuits-1

#### 58. (c)

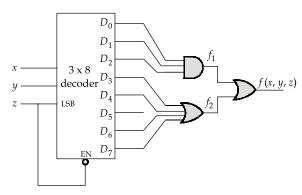

The given  $3 \times 8$  decoder is active low output type. The circuit can be redrawn as shown in the figure below:

If z = 1, then decoder is disabled and all outputs  $D_0$ - $D_7$  are 0. If z = 0, then EN = 1 (Since input LSB = 0, we will get output only for even values)

The outputs  $D_{0'}$   $D_{2'}$   $D_4$  and  $D_6$  are active and outputs  $D_{1'}$   $D_3$ ,  $D_5$  and  $D_7$  are inactive.

We have,  $f_1 = D_3 + D_4 + D_6 + D_7$ . Since  $D_3$  and  $D_7$  remain inactive, we have,  $f_1 = \Sigma m(4, 6)$ .

Here,  $f_2 = 0$  because all three inputs  $D_0$ ,  $D_1$  and  $D_2$  can never be 1 at the same time.

Thus,

$$f(x, y, z) = f_1 + f_2 = \sum m(4, 6)$$

# 59. (c)

Output =

$$\overline{A}\overline{B} + A\overline{B} + \overline{A}B$$

=  $\overline{A} + \overline{B}$

#### 60. (a)

$$F = (A+B)(A+\overline{A}+\overline{B})C+\overline{A}(B+\overline{C})+\overline{A}B+ABC$$

=  $AC+BC+\overline{A}B+\overline{A}\overline{C}+\overline{A}B+ABC$

=  $AC+BC+\overline{A}(B+\overline{C})$

Using K-map, we get

$$F = AC + \overline{A}B + \overline{A}\overline{C}$$

# MADE EASY

61. (d)

> : Both the inputs of the Ex-NOR gate can never be equal since only one output of the decoder circuit will be active at a time. So, *f* is always equal to zero.

62.

Two TTL gates with "open-collector" outputs directly connected together, function as a "wired AND" logic gate.

Thus,

$$f = (\overline{AB})(\overline{CD}) = (\overline{A} + \overline{B})(\overline{C} + \overline{D})$$

63. (d)

Given that,

$$f(A, B, C) = \Pi M(1, 3, 4, 5) = \Sigma m(0, 2, 6, 7)$$

Now,

- $\therefore$  Required inputs are,  $I_0 = \overline{A}$ ,  $I_1 = 0$ ,  $I_2 = 1$  and  $I_3 = A$

- 64. (b)

$$(09)_{10} \xrightarrow{\text{Excess-3}} 1001 + 0011 = 1100$$

$$(09)_{10} \xrightarrow{\text{BCD}} 1001$$

$$(10)_{10} \xrightarrow{\text{Gray Code}} 1111$$

$$(10)_{10} \xrightarrow{\text{Binary Code}} 1010$$

65. (b)

From the given  $8 \times 1$  MUX,

$$Y(A, B, C) = \overline{A}\overline{B}\overline{C}(1) + \overline{A}\overline{B}C(1) + \overline{A}B\overline{C}\overline{D} + \overline{A}BC(0) + A\overline{B}\overline{C}(1) + A\overline{B}C(0) + AB\overline{C}(\overline{D}) + ABC(0)$$

$$= \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}C + \overline{A}B\overline{C}\overline{D} + A\overline{B}\overline{C} + AB\overline{C}\overline{D}$$

$$Y(A, 1, C) = \overline{A}\overline{C}\overline{D} + A\overline{C}\overline{D} = \overline{C}\overline{D}$$

66. (c)

> A reflexive code is a code where the code for 9 is the complement of code for 0 and so on. Ex:

Excess-3 code for 9:1001+0011=1100

Excess-3 code for 0:0000 + 0011 = 0011 which is complement of code for 9.

A sequential code is a code where each succeeding code is one binary number more than the preceeding code. Excess-3 code satisfies both these properties.

Given,

$$F(P, Q) = ((0 + P) \oplus (1 + Q)) \oplus ((1 + Q) \oplus (P \oplus Q))$$

$$= (P \oplus \overline{Q}) \oplus (\overline{Q} \oplus (P \oplus Q))$$

$$= (P \oplus \overline{Q}) \oplus ((\overline{Q} \oplus P) \oplus (\overline{Q} \oplus Q))$$

$$= (P \oplus \overline{Q}) \oplus ((\overline{Q} + P) \oplus 1)$$

$$(P \oplus \overline{Q}) \oplus (\overline{P} \oplus \overline{Q})$$

$$= (P \oplus \overline{Q}) \oplus (\overline{P \oplus \overline{Q}})$$

$$F(P, Q) = 1$$

$$\overline{F}(P,Q) = 0$$

#### 68. (d)

*:*.

Given,

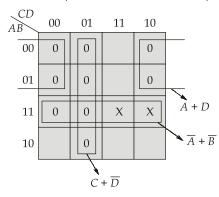

$$f(A, B, C, D) = \sum m\{3, 7, 8, 10, 11\} + \sum d\{14, 15\}$$

=  $\pi(0, 1, 2, 4, 5, 6, 9, 12, 13) \pi d\{14, 15\}$

$$f = (A+D)(\overline{A}+\overline{B})(C+\overline{D})$$

Given,

$$F = (X + Y + Z)(\overline{X} + Y)(\overline{Y} + Z)$$

$$\overline{F} = \overline{(X + Y + Z)(\overline{X} + Y)(\overline{Y} + Z)}$$

$$= (\overline{X + Y + Z}) + (\overline{\overline{X} + Y}) + (\overline{\overline{Y} + Z})$$

$$= \overline{X}\overline{Y}\overline{Z} + X\overline{Y} + Y\overline{Z}$$

$$= \overline{Y}(X + \overline{X}\overline{Z}) + Y\overline{Z}$$

$$= \overline{Y}(X + \overline{Z}) + Y\overline{Z} = X\overline{Y} + \overline{Z}$$

70. (c)

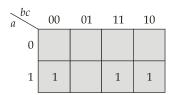

$$Z = a(b + \overline{c})$$

$$Z = ab + a\overline{c}$$

Representing the Boolean expression on K-Map,

$$Z(a, b, c) = \Sigma m(4, 6, 7)$$

# 71. (d)

:.

Let output of XOR gate be f',

$$f' = f_1 \oplus f_2$$

$$= \sum m(0, 1, 4, 8, 13) \oplus \sum m(2, 6, 14, 15)$$

$$f' = \sum m(0, 1, 2, 4, 6, 8, 13, 14, 15)$$

The output of EXNOR gate,

$$f = f_1 \odot f_3$$

=  $\Sigma m(0, 1, 2, 4, 6, 8, 13, 14, 15) \odot \Sigma m(4, 8, 13, 15)$

$f = \Sigma m(4, 8, 13, 15)$

#### 72. (c)

Excess-3 code can be obtained by adding 3 to each decimal digit, and obtain the corresponding 4-bit binary number.

Given, Excess-3 number,

$$\frac{1100}{C} \frac{1010}{A} \frac{0011}{3} \cdot \frac{0111}{7} \frac{0101}{5}$$

The binary code from given Excess-3 code can be obtained as,

$\therefore$  The decimal equivalent is  $(100101110000 \cdot 01000010)$

$$= (970.42)_{10}$$

#### 73. (c)

*:*.

Truth Table for 2-to-4 decoder:

$$Y_0 = \overline{A}\overline{B}; \quad Y_1 = \overline{A}B$$

$$Y_2 = A\overline{B}; \quad Y_3 = AB$$

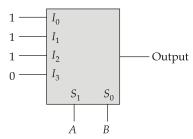

$$F(A, B, C, D) = \overline{S_1}\overline{S_0}I_0 + \overline{S_1}S_0I_1 + S_1\overline{S_0}I_2 + S_1S_0I_3$$

$$= \overline{C}\overline{D}(\overline{A}\overline{B}) + \overline{C}D(0) + C\overline{D}(1) + CD(AB)$$

$$= \overline{A}\overline{B}\overline{C}\overline{D} + C\overline{D} + ABCD$$

By using 4-variable K-map,

| AB $CD$ | 00 | 01 | 11 | 10 |

|---------|----|----|----|----|

| 00      | 1  |    |    | 1  |

| 01      |    |    |    | 1  |

| 11      |    |    | 1  | 1  |

| 10      |    |    |    | 1  |

$$F(A, B, C, D) = \Sigma m(0, 2, 6, 10, 14, 15)$$

74. (d)

*:*.

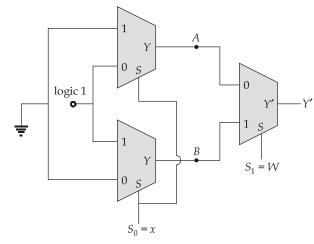

output,

$$A = \overline{S}_0(1) + S_0(0) = \overline{x}(1) = \overline{x}$$

output,

$$B = \overline{S}_0(0) + S_0(1) = x$$

output

$$Y' = \overline{S_1}A + S_1B = \overline{W}\overline{x} + Wx$$

$Y' = W \odot x$ , which represents XNOR logic.

75. (b)

ROM is a non-volatile memory which retains its data even when power is turned off. Both statement (I) and (II) are correct and statement (II) is not the correct explanation of statement (I).

0000