# MADE EASY

India's Best Institute for IES, GATE & PSUs

# **ESE 2019 : Mains Test Series**

UPSC ENGINEERING SERVICES EXAMINATION

#### **Electronics & Telecommunication Engineering**

Test-2: Network Theory + Microprocessors and Microcontroller

Digital Circuits-1 + Control Systems-1

| Name :      |        |           |               |          |                     |

|-------------|--------|-----------|---------------|----------|---------------------|

| Roll No :   | E C 1  | 9 M B     | DLA =         | 794      |                     |

| Test Centre | es     |           |               |          | Student's Signature |

| Delhi       | Bhopal | Noida 🗌   | Jaipur 🗌      | Indore 🗌 |                     |

| Lucknow 🗌   | Pune 🗌 | Kolkata 🗌 | 8hubaneswar 🗌 | Patna 🗌  |                     |

| Hyderabad 🗌 |        |           |               |          |                     |

#### **Instructions for Candidates**

- Do furnish the appropriate details in the answer sheet (viz. Name & Roll No).

- 2. Answer must be written in English only.

- 3. Use only black/blue pen.

- The space limit for every part of the question is specified in this Question Cum Answer Booklet. Candidate should write the answer in the space provided.

- Any page or portion of the page left blank in the Question Cum Answer Booklet must be clearly struck off.

- Last two pages of this booklet are provided for rough work. Strike off these two pages after completion of the examination.

| CE USE                                |  |  |

|---------------------------------------|--|--|

| Marks Obtained                        |  |  |

| n-A                                   |  |  |

| 41                                    |  |  |

| _                                     |  |  |

| _                                     |  |  |

| 40                                    |  |  |

| on-B                                  |  |  |

| 48.                                   |  |  |

| 42                                    |  |  |

|                                       |  |  |

| .45                                   |  |  |

| (216)                                 |  |  |

| ֡֡֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜֜ |  |  |

· V. Good handwritting-

Signature of Evaluator

Cross Checked by

Corp. office: 44 - A/1, Kalu Sarai, New Delhi-16 | Ph: 011-45124612, 9958995830 | Web: www.madeeasy.in

#### Section A: Network Theory + Microprocessors and Microcontroller

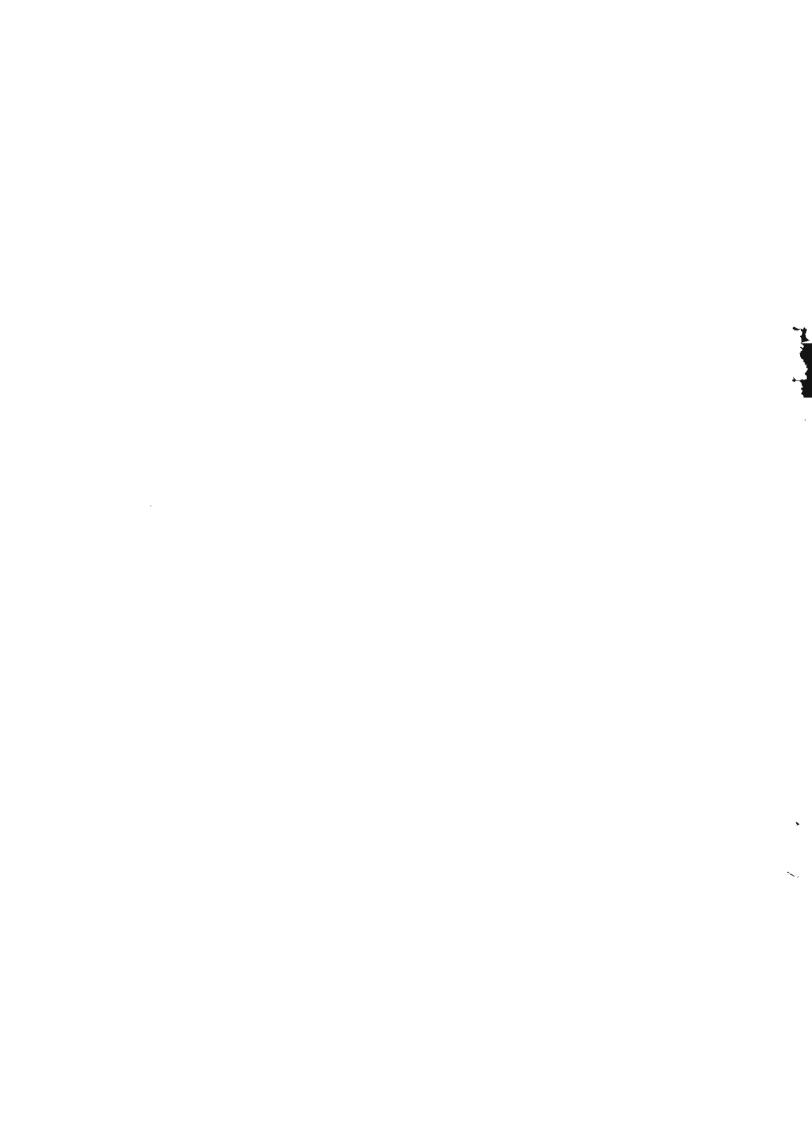

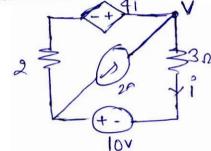

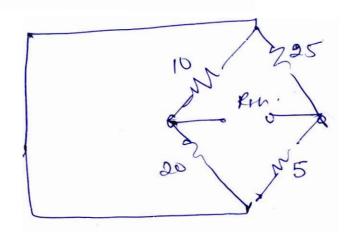

Q.1 (a) Consider the circuit shown below:

Determine the output voltage  $(V_0)$ , output current  $(I_0)$  and voltage gain  $(V_0/V_i)$ .

[12 marks]

Determine the output voltage

$$(V_0)$$

, out  $I_1 = \frac{10}{8} \text{ Amp}$

$$V_1 = \frac{10}{8} \times 6 = 7.5 \text{ Amp}$$

$$V_1 = 7.5 \times 4 = 30 \text{ Amp}$$

$$I_2 = 3 \times 30$$

$$I_3 = 10 \text{ Amp}$$

$$V_3 = 10 \text{ Amp}$$

$$V_4 = 7.5 \times 4.5 \times$$

$$J_0 = \frac{45}{15}$$

$$V_0 = 10 \times 2$$

$$Voltage a ain = \frac{Vo}{Vi} = \frac{To \times 10}{Vi}$$

$$\frac{V_0}{V_i} = \frac{3x10}{10}$$

$$\frac{V_0}{V_i} = 3$$

50 output -i

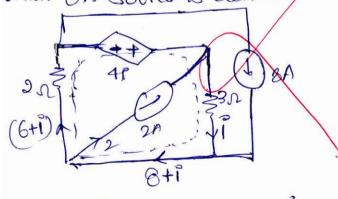

Q.1 (b)

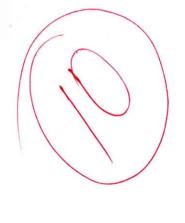

For the circuit shown in the figure below, find the current (i), using superposition theorem.

tov source is active

[12 marks]

Model at v  $\frac{V-4i^{2}}{2} + \frac{V+10}{3} = 2 - 1$

$$-\frac{10-1}{2} + 1 = 2$$

$$-10-1+21 = 4$$

11 = 14 Amp SD

When 8A source is active

KVI in dottole line -4i+3i+2(6+i)=0-1+12+21 =0

1=-12 Amp

$$|SO| = |I_1 + |I_2|$$

$$|SO| = |SO| = |SO|$$

$$|SO| = |SO|$$

$$|SO| = |SO| = |SO|$$

$$|SO| = |SO$$

E&T

#### MADE EASY Question Cum Answer Booklet

Page 5 of 71

Do not write in this margin

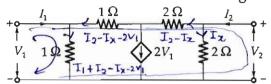

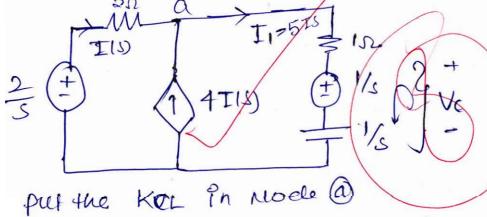

Q.1 (c)

Obtain Z-parameter matrix for the circuit shown in the figure below:

[12 marks]

801-

from the diagram

$$-V_1 + J_1 + J_2 - J_2 - 2V_1 = 0$$

$$\boxed{+3V_1 = I_1 + I_2 - I_x} - \boxed{\phantom{-}}$$

KVL at dotted line

$$-V_1 - I(I_2 - I_2 - 2V_1) - 2(I_2 - I_x) + V_2 = 0$$

$$V_1 + T_2 - I_2 - 2V_1 + 2T_2 - 2T_2 - V_2 = 0$$

$$T_{\chi} = -\frac{V_1 + 3T_2 - V_2}{3}$$

put 3 Pn D

$$V_2 = \frac{2}{3} \left[ -V_1 + 3I_2 - V_2 \right]$$

$$V_2 = -\frac{2}{3}V_1 + 2T_2 - \frac{2}{3}V_2$$

$$\frac{5}{3}V_2 = -\frac{2}{3}V_1 + 2T_2$$

$$\sqrt{2 = -2\sqrt{1+6T_2}} - \Phi$$

$$3V_1 = T_1 + T_2 - \left[ \frac{-V_1 + 3T_2 - V_2}{3} \right]$$

$$\frac{8}{3}$$

V<sub>1</sub> =  $\frac{\sqrt{1}}{3}$  +  $\frac{1}{3}$

$$8 V_1 = -\frac{2V_1 + 6T_2}{5} + 3T_1$$

$$40V_1 = -2V_1 + 6T_2 + 15T_1$$

$$V_{2} = -2\left[\frac{15}{92}T_{1} + \frac{15}{92}T_{2}\right] + 6T_{2}$$

$$V_2 = -\frac{15}{21}T_1 - \frac{6}{21}T_2 + 6T_2$$

$$V_{2} = -\frac{15}{21} I_{1} - \frac{6}{21} I_{2} + 6 I_{2}$$

$$V_{2} = -\frac{15}{21} I_{1} + \frac{126}{21} I_{2}$$

$$V_{2} = -\frac{15}{21} I_{1} + \frac{126}{21} I_{2}$$

$$V_2 = -\frac{3}{21}I_1 + \frac{24}{31}I_2 + \frac{8}{7}I_2$$

Do not

write in

this margin

#### **EPSY** Question Cum Answer Booklet

Consider the following subroutine program of an 8085 microprocessor, which is Q.1(d)operating with a clock frequency of 2 MHz:

Let "N" is the decimal equivalent of the DATA\_8 bit stored in B register. By analyzing the above program, derive an expression for the overall time delay produced by the subroutine. Using the result obtained, determine the value of "N" required to produce the overall time delay of 70 µs.

[12 marks] as over all delay = 7T+ NX4T+ [(N-1) 10T+ +7T] +10T = (10AA)T+ ATN+10NT-16T+AT = (10AA)T+ ATN+10NT-16T+AT =) (14+14H)T felkok = 20012 T2 1 11800 SO Delay = (14+14H) 1/2 USEC = (7+7H) USEC = 7 ( 1+N) MSee to provide the overlall delay of 704%.

70 use = A(N+1) Me

N+1=10

N=9

to Roduce the overall delay of Foursee we required the N should be

Q.1 (e) Differentiate between embedded and general purpose computing systems.

[12 marks]

Embedded System General purpose system 9t is consist of Hardward 91 is one of the system ultichis consist of as avellas software Handwire and saffwine part. There is NO Ose of DMA in along with DMA. this system Slow as compane to 9t is very fast as. embedded system. compare to others. No direct Memor Direct memory dransfer transfer. through DonA. very slow Response. 9+ is having high speed. dess complex as the Mere complex Mumber of component-Ifstem then 13 Less. coest of the embedde Relatively less cost System is more as we dote not using compare to General DMA controller. purpode system Less Number of Large Number of features are features are avuilable available in

In the embedded

Page 10 of 71

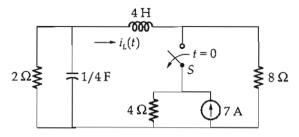

Q.2 (a) In the circuit shown in the figure below, the switch S is closed for a long time and opened at t = 0. Find the time domain expression of the current  $i_L(t)$  for t > 0.

[20 marks]

Page 12 of 71

Q.2 (b) The reduced incidence matrix of a linear graph is given below:

$$A = \begin{bmatrix} 1 & 2 & 3 & 4 & 5 & 6 & 7 \leftarrow Branches \\ 0 & 0 & 1 & 1 & 1 & 0 & -1 \\ 0 & 1 & 0 & 0 & -1 & 1 & 1 \\ -1 & 0 & -1 & 0 & 0 & -1 & 0 \end{bmatrix}$$

The branches [2, 3, 4] constitute a tree.

- (i) Without drawing the graph, determine the f-cutset matrix  $Q_C$ .

- (ii) Determine the number of trees possible for the graph.

- (iii) Draw the graph and verify the result for  $Q_C$ .

[20 marks]

Page 15 of 71

Page 16 of 71

Q.2 (c)

(i) Complete the following table by indicating the logic level (1 or 0) on each control or status pin of 8085 microprocessor for various machine cycles shown.

| Machine Cycle | RD | WR | IO/M | $S_1$ | $S_0$ |

|---------------|----|----|------|-------|-------|

| Memory read   |    |    |      |       |       |

| Memory write  |    |    |      |       |       |

| I/O read      |    |    |      |       |       |

| I/O write     |    |    |      |       |       |

| Opcode fetch  |    |    |      |       |       |

| Halt          |    |    |      |       |       |

|               |    |    |      |       |       |

(ii) Draw the timing diagram of data flow when the 8085 instruction MOV C, A (machine code 4FH), stored in the memory location 2005H, is being fetched.

[8 + 12 marks]

Page 18 of 71

Q.3 (a)

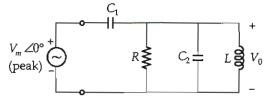

Consider the circuit shown in the figure below:

- (i) Derive an expression for the resonant frequency of the above circuit.

- (ii) If  $V_m = 10 \text{ V}$ ,  $R = 1 \text{ k}\Omega$ ,  $C_1 = 2 \text{ nF}$ ,  $C_2 = 8 \text{ nF}$  and L = 5 mH, then determine the effective value of the voltage  $V_0$  at resonant frequency by using the result obtained in part (i). [25 marks]

Page 20 of 71

Page 21 of 71

Page 22 of 71

Page 23 of 71

Do not write in this margin

Q.3 (b)

Assuming the microprocessor is completing an RST7.5 interrupt request, check to see if RST6.5 is pending. If it is pending, enable RST6.5 without affecting any other interrupt; otherwise, return to the main program.

[15 marks]

Page 24 of 71

Page 25 of 71

Do not write in this margin

Q.3 (c)

Write an 8085 assembly language program to arrange a data array in ascending order. The array is stored from the memory location 2501H and the length of the array is stored at 2500H. The resultant array should be stored from the memory location 2601H. Assume that the numbers in the data array are represented in unsigned 8-bit format.

[20 marks]

Page 26 of 71

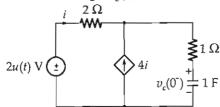

Q.4 (a)

(i) In the circuit shown below, the initial voltage across the capacitor is  $v_c(0^-) = 1 \text{ V}$ . Find the expression of the voltage  $v_c(t)$  for t > 0.

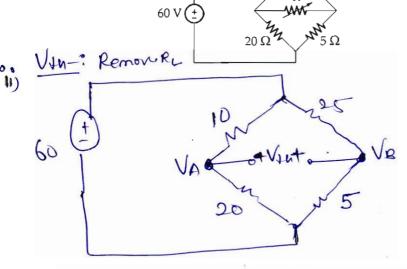

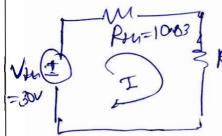

(ii) Determine the maximum power that can be delivered to the variable resistor *R* in the circuit shown below.

[13 + 12 marks]

$$V_{A} = \frac{60 \times 10}{36} \Rightarrow 20 \text{ With}$$

$$V_{B} = \frac{25 \times 60}{36} \Rightarrow 50 \text{ Volt}$$

$$V_{H} = 50 - 20 \quad \text{Van} = 30 \text{ Vol}$$

$$R_{h}=1003$$

$R_{h}=1003$

$R_{h}=10.8320$

So power =

$$\frac{V + n^2}{4R} = \frac{(80)^2}{4 \times 10.83}$$

$$\frac{(80)^2}{4\times10.83} = 20.775W$$

convert înto Laplace domain

$$T_1 = T_1(S) + U_1T_1(S) = 5T_1(S)$$

Kerat Modo@

$$J(s) + 4J(s) = \frac{Va - 1/s}{1 + 1/s}$$

$$5 \pi s = \frac{\sqrt{a-1/c}}{\frac{s+1}{s}} = \frac{s\sqrt{a-1}}{s+1}$$

$$Va = \frac{1}{5} [1 + 5 I(s) (s+1)]$$

KUL at out koop

$$-\frac{2}{5} + 2\Gamma(5) + 5F(5) + \frac{1}{5} + \frac{5F(5)}{5} = 0$$

$$T(S) \left[ 2+5+\frac{5}{S} \right] = \frac{1}{5}$$

$$T(S) = \frac{(1/S)}{7+5} = \frac{1}{7S+5}$$

For  $OC$

KUL FOR DC

$$\frac{1}{7} = A(S+5/7) + BS S=0$$

$$A=5$$

$$S>-5/7$$

$$V(CLS) = \frac{1}{S} + \frac{5}{S} - \frac{5}{S+5/4}$$

Where  $\frac{1}{S}$  we have the  $\frac{1}{S}$

$$V(15) = \frac{6}{5} = \frac{5}{517} + \frac{4}{100} = \frac{5}{5} = \frac{5}{17} + \frac{5}{17} = \frac{5}{17} = \frac{5}{17} + \frac{5}{17} = \frac$$

Page 30 of 71

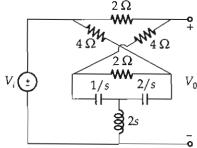

Q.4 (b)

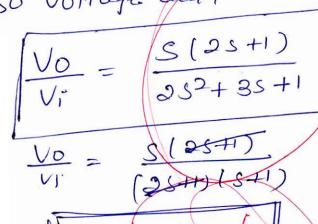

For the network shown in the figure below, find the voltage gain  $V_0 / V_i$ .

Solution

[15 marks]

$$\frac{4^{11}}{4^{11}} = \frac{4+2}{2} = \frac{4-2}{2}$$

$$\frac{4-2}{2} = \frac{4+2}{2} = \frac{4-2}{2}$$

$$\frac{4-2}{2} = \frac{4+2}{2} = \frac{4+2}{2}$$

$$Z_2 = \begin{bmatrix} 1/5 + 25 & 25 \end{bmatrix}$$

$$\begin{cases} 25 & 25 + \frac{2}{5} \end{cases}$$

$$50 \quad 2eq = 21+22 = 3 \quad 1 \quad \frac{1}{5}+25 \quad 25 \quad 25+25 \quad 35+25 \quad$$

$$\frac{2 + 2 + 3}{5} = \frac{2 + 2 +$$

Page 32 of 71

Do not write in this margin

$$\frac{Vo}{Zo} = I_1$$

$$\frac{\sqrt{0}}{\sqrt{1}} = \frac{221}{211}$$

put the value from

$$\frac{\sqrt{0}}{\sqrt{1}} = \frac{2s+1}{2s^2+3s+1}$$

$$\frac{\sqrt{0}}{\sqrt{8}} = \frac{2\sqrt{2}+\sqrt{5}}{2\sqrt{5}^2+3\sqrt{5}+1}$$

SD Voltage Cacein

Do not write in

this margin

#### **EPSY** Question Cum Answer Booklet

Q.4 (c)

(i) Explain different addressing modes of 8086 microprocessor for sequential control flow instructions, with an example for each addressing mode.

Ans-i

(ii) Write a short note on the flag register of 8086 microprocessor. 8086 supports large number of additionarks 1) Immediate Toppe of addressing mode -

In this type of addressing mode data is very immediate to addressing mode.

MON AX, QOIOH; 5 xample In this Instruction the data will move to AX/and store In that accumulator.

2) Direct addressing roode -: In this type of addressing mode does is directly in the instruction part only.

Example - mov Ax [OOIOH]; In this instruction the memory, content of [ODIOH] WILL be move to AX Register.

3) Register-Register addressing. mode -3 In this type of addressing mode the Confert of one register will be move to amother Register.

Example MOV AX, BX;

Page 34 of 71

In the above Prstruction the content of Bx Register will move to Ax Register.

1) Register Indirect addressing mode -3 In this addressing mode the content of one Register memory Location will be move to another pegister.

Example. Mov Ax [BX];

9nthis Prestruction the data from memory Location of Bx will be more to RegisterAX.

(5) Index addressing mode In this addressing mode the content of SI mes will be more to Register Example -: mov Ax, [SI]

- 6) Base Index addressing mode.

- Register index addressing mode

Hog Register in 8086-

1/X /X /X /TF / TF / DF /S /Z/X

Namous types of Flog present in 8086.

رآل

Sign Flag-i 9t is one type of Flag which is Wed to represent the sign magnitude of output if after operation 1 means Negertive Number.

Parity Flag. 8086 Follows even parity exheme.

If the Number of 1' present in the output

1's even then it will be treated as 1' others

Wise. zero.

Early flag- 9+ represent the comy ofter performing of operation. It represent the comy at msp side.

Zero flag ? When after operation, behin the out is a thren it will be as I' other wise it will be o:

AUXITIONY Flog -?

It will be represented by the Auxillary Carry flog.

Trap flag-: It is applicable when.

Has markable interrupt occurs.

direction flag mas &

#### Section B: Digital Circuits-1 + Control Systems-1

Q.5 (a)

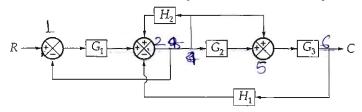

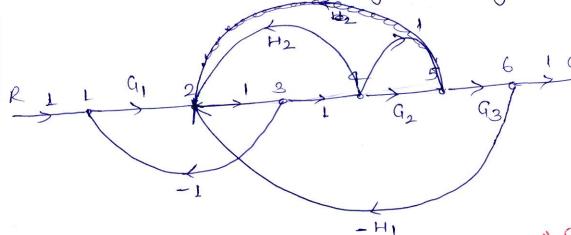

Find transfer function for the block diagram shown in the figure below:

[12 marks]

Sol-:

As we can convert into signal Plow graph.

Forward path Cecin = G162 G8, Girgo

Individual Loops SI= - GI

$$TF = \begin{cases} G_1 G_2 G_3 + G_1 G_3 \\ V - G_1 + H_2 - G_3 H_1 - G_1 G_3 H_1 \end{cases}$$

$$TF = \begin{cases} G_1 G_3 G_2 + 1 \\ G_1 - H_2 + G_3 H_1 + G_1 G_3 H_1 \end{cases}$$

Q.5 (b)

The transfer function of a first order control system is  $T(s) = \frac{K}{(s+a)}$ . When a step input is

applied, the system response reaches 50% of its steady state value in 5 sec. Find the time required by the same response to reach 90% of steady state value.

Sol -:

$$\frac{C(S)}{R(S)} = \frac{K}{S+\alpha} \qquad C(S) = \frac{K}{S(S+\alpha)} = \frac{A}{S} + \frac{B}{S+\alpha}$$

[12 marks]

$$K = A(S+\alpha) + BS$$

$$S = 0$$

$$A = \frac{k}{\alpha} \qquad S = -\alpha$$

$$C(S) = \frac{k}{\alpha} - \frac{K}{3} - \frac{K}{3}$$

$$S = -\alpha$$

$$S = -$$

Inverse Laplace Transform

C(+)=

$$\frac{K}{a}\left[1-e^{-at}\right]$$

wh)  $-0$

$$C(\alpha) = \frac{K}{\alpha}$$

$$\frac{1}{2} = 1 - e^{-9 \times 5}$$

$$\frac{1}{2} = e^{-\alpha \times 5}$$

$$a = 0.138$$

$$t = \frac{2.302}{\alpha}$$

$$t = \frac{2.302}{0.138}$$

So to Reach 90% of Steady state value we required 16.68 see.

Q.5 (c)

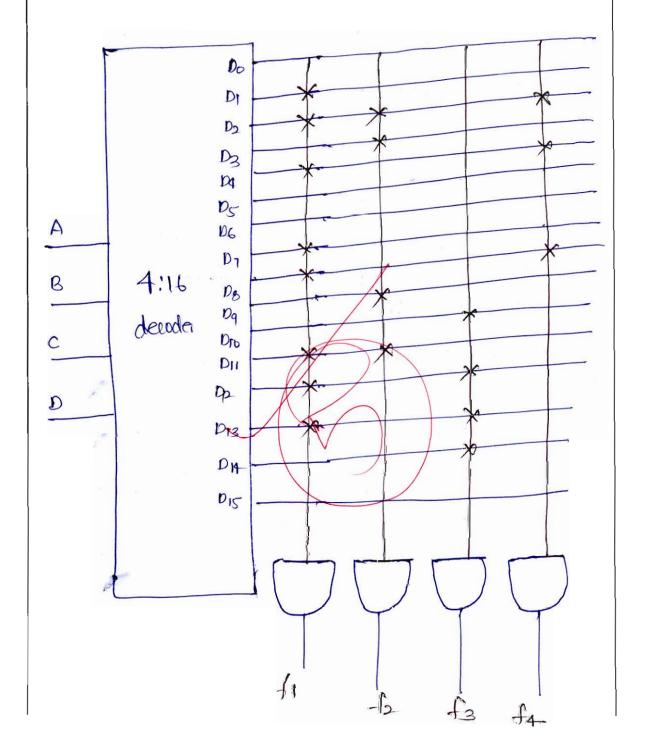

(i) Implement the following multiple output combinational logic circuit using 4-line to 16-line decoder.

$$f_1 = \Sigma m(1, 2, 4, 7, 8, 11, 12, 13)$$

$$f_2 = \Sigma m(2, 3, 9, 11)$$

$$f_3 = \Sigma m(10, 12, 13, 14)$$

$$f_4 = \Sigma m(2, 4, 8)$$

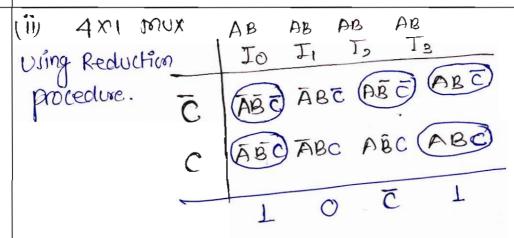

(ii) Implement  $f(A, B, C) = \sum m(0, 1, 4, 6, 7)$  using a  $4 \times 1$  MUX by connecting A and B to its select lines.

[6 + 6 marks]

## 4:16 decoder

80 using 4x1 mux and Al Bas

the select Line

Digital chrevit diagram—:

E&T

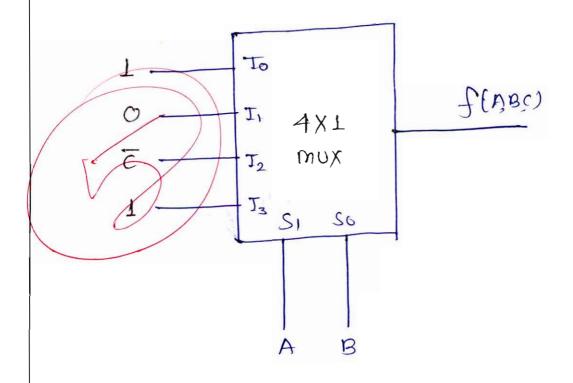

Q.5 (d)

Design a combinational circuit that accepts a 3-bit number and generates an output binary number equal to the square of the input number using a 8 × 4 ROM circuit.

| TruthTable |   |   |   | Owput |    |            |    |    | [12 marks] |  |

|------------|---|---|---|-------|----|------------|----|----|------------|--|

|            | A | B | C | 1 70  | bi | ba         | pa | 64 | b5         |  |

| ٠          | 0 | 0 | 0 | 0     | 0  | 0          | 0  | 0  | 0          |  |

|            | 0 | 0 | 1 | 0     | 0  | D          | 0  | 0  | 1          |  |

|            | 0 | 1 | 0 | 0     | 0  | 0          | F  | 0  | 0          |  |

|            | 3 | 1 | 1 | 0     | 0  | L          | 0  | 0  |            |  |

|            | L | 0 | 0 | 0     | 1  | $\bigcirc$ | 0  | 0  | 0          |  |

|            | 1 | 0 | 1 | 0     | 1  | 1          | 0  | 0/ | 1          |  |

|            | 1 | 1 | 0 | 1     | 0  | 0          |    | 0  | 0          |  |

|            | 1 | 1 | 1 | ł     | L  | 0          | 6  | 0  | 7          |  |

| ,          |   |   |   |       |    | 1          |    | 1  |            |  |

cus the touth Houste of Binary number.

equal to the square of y the input Number.

Using 8X4 ROM.

23×4

n=3

so we can use 3:8 decoder

Acked to denon upls 8x4 Q.5 (e)

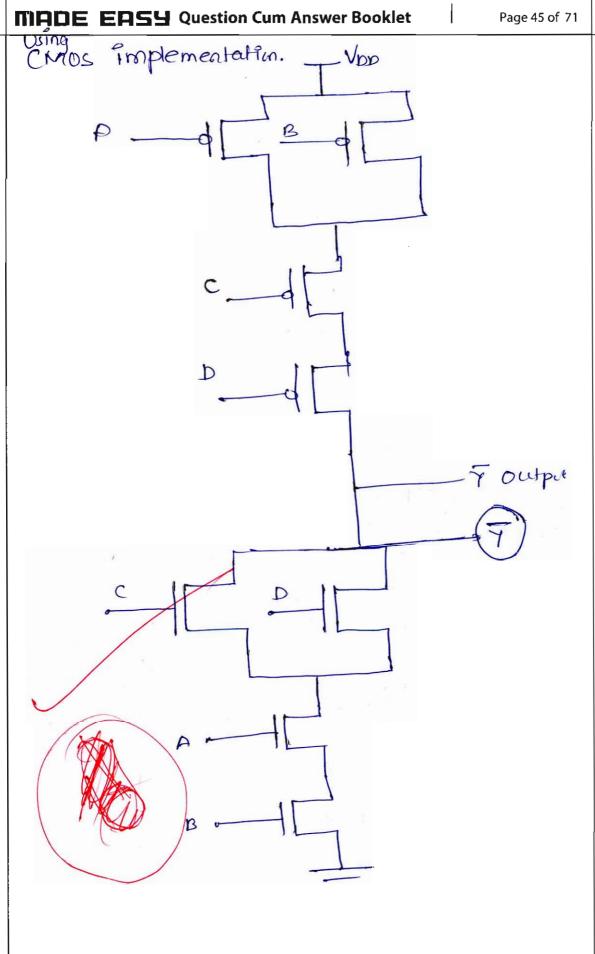

Design CMOS logic circuits to implement the following expressions:

(i)

$$Y = \overline{A + B(C + D)}$$

(ii)

$$Y = \overline{A} + \overline{B} + (\overline{C} + \overline{D})$$

(i)  $\overline{y} = A + B(C+D)$

[6 + 6 marks]

A+B = AB

(ii)

$$Y = \overline{A} + \overline{B} + \overline{C} + \overline{D}$$

$$Y = \overline{A} + \overline{B} + \overline{C} + \overline{D}$$

$$Y = \overline{A} + \overline{B} + \overline{C} + \overline{D}$$

$$Y = \overline{A} + \overline{B} + \overline{C} + \overline{D}$$

$$= \overline{A} + \overline{C} + \overline{D}$$

Q.6 (a)

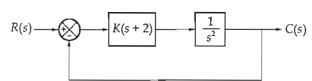

(i) Consider the block diagram shown below:

Determine the value of K such that the phase margin of the system is 50°.

(ii) A negative feedback control system has open loop transfer function,

$$G(s)H(s) = \frac{K(s+2)}{s(s-1)}$$

Find the value of system gain K so that the damping ratio of the system is  $\frac{1}{\sqrt{5}}$

[12 + 8 marks]

Colution.

$$S(S-1) + K(S+2) = 0$$

square on both side

$$4K = K^2 + 1 - 2K$$

So Gain value K = 5.028 and 0.171

(i) GHIO=

$$\frac{K(S+2)}{S^2}$$

Phase margin = 50 = 180+ [ Gija)

Cejw = -130

$$K(\sqrt{w^2+2}) = (-180^\circ + + tom) (\frac{w}{2})$$

$$ter \left(\frac{\omega}{a}\right) = 50^{\circ}$$

$$W=2 \times tenso$$

$$\frac{K\sqrt{\omega^2+4}}{\omega^2} = 1$$

$$\omega = 2.382$$

$$K = \frac{\omega^2}{\sqrt{\omega^2 + 4}} = \frac{(2.382)^2}{\sqrt{(2.382)^2 + 4}} = \frac{5.679}{3.114}$$

SO [k=1.822] we will get phase morgin of 50° Q.6 (b)

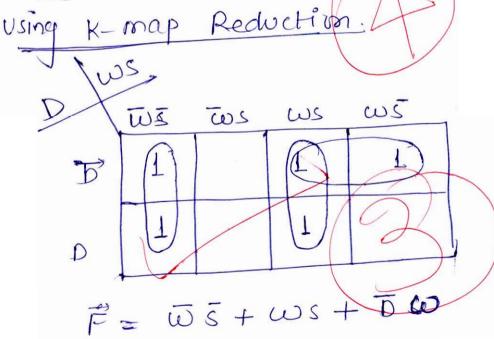

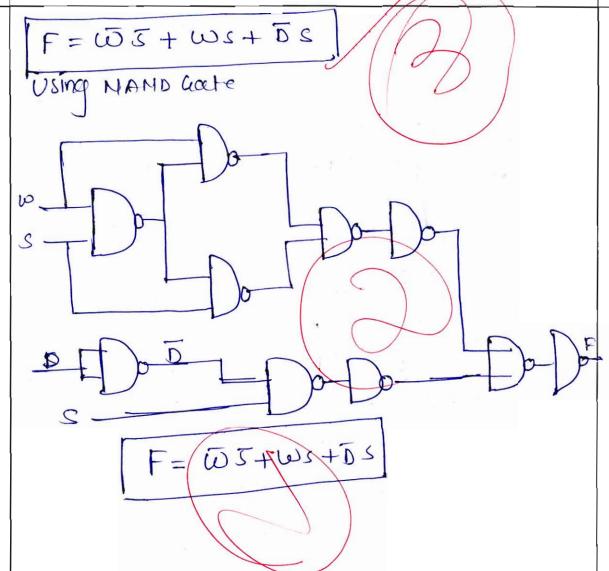

In a power plant, three digital signals: drum level (D), water flow (W) and steam temperature (S) are used to control a particular system by a feedback signal (F) that comes from the field to the control room.

Find the minimised logic expression that generates a high feedback signal (F) whenever any one of the conditions is satisfied.

$C_1$ : All the levels are at zero.

$C_2$ : Level D and S set to zero.

$C_3$ : Level W and S set to zero.

$C_4$ : Level D set to zero.

$C_5$ : All the levels are high.

(ii) Draw the logic circuit using the expression obtained in part (i) that generates a high feedback (F), using only two-input NAND gates.

from the Colven condition -> [15 + 5 marks]CI DWS -Consider Caro Dws  $\rightarrow$  2 D-ms E Caro Dws  $\rightarrow$  3 Caro Dws  $\rightarrow$  3 C5  $\rightarrow$  Dws  $\rightarrow$  7 DIMSB

from the Given condition.

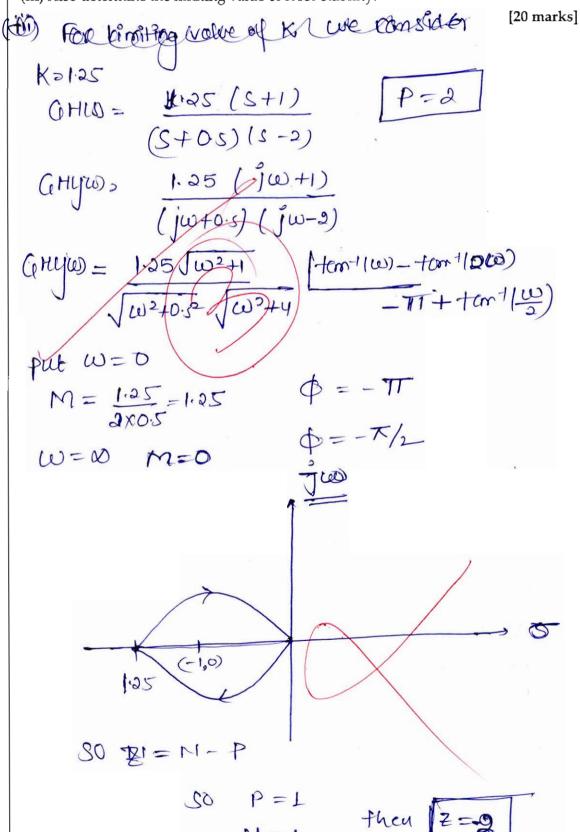

Q.6 (c)

Using Nyquist criterion investigate the closed-loop stability of the system whose open-loop transfer function is,

$$G(s) \ H(s) = \frac{K(s+1)}{(s+0.5)(s-2)}$$

For (i) K = 1.25 and (ii) K = 2.5

(iii) Also determine the limiting value of K for stability.

SO For K=1.25 System is Unstable system.

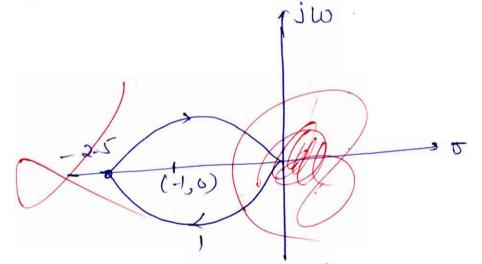

(ii)

for K= 25

tomition - tomion - IT+ GHUW) = D.5 W2+1 tan (0/2).

W=0

M=Q.5

W=X

M=0  $\phi=-1/2$

using polar Part followed by Myquist pld

M=-1 Wock wise 50

Stable For K=2-5

to apendoop pole lies on Right side of S-plane. Stable system.

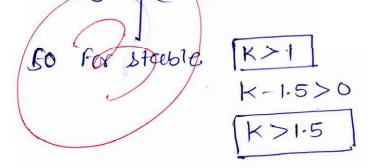

(iii) For limiting value of 'K'

$$1 + Gr(0) = 0$$

$(S + 0.5) + (S + 0) = 0$

$S^2 - 2S + 0.5S - L + KS + K = 0$

$C^2 - 1.5S + KS + (K - 1) = 0$

$$S^2 - 1.5S + KS + (K-1) = 0$$

$S^2 + S(K-1.5)S + (K-1) = 0$

SO if [K>1.5] then system is stable.

Q.7 (a)

A unity feedback control system has an open loop transfer function,

$$G(s) = \frac{K\left(s + \frac{4}{3}\right)}{s^2(s+12)}$$

Sketch the complete root locus. Also, find the value of *K* for which all roots are equal, what is the value of these roots?

[20 marks]

Page 55 of 71

Do not write in this margin

Page 56 of 71

Do not write in this margin

Page 57 of 71

Do not write in this margin

Q.7 (b)

A switching circuit has two control inputs ( $C_1$  and  $C_2$ ), two data inputs ( $X_1$  and  $X_2$ ) and one output (Z). The circuit performs one of the logic functions AND, OR, XOR, XNOR depending upon the control inputs. The output is equal to  $X_1 + X_2$  for  $C_1C_2 = 00$ ;  $X_1 \oplus X_2$  for  $C_1C_2 = 01$ ;  $X_1X_2$  for  $C_1C_2 = 10$ ; and  $X_1 \odot X_2$  for  $C_1C_2 = 11$ . Find all the possible minimal expressions for logic function Z.

[20 marks]

Page 58 of 71

Do not write in this margin

Page 59 of 71

Do not write in this margin

Page 60 of 71

Do not write in this margin

Q.7 (c)

Design combinational circuits for the following Boolean functions as instructed.

- (i) Implement  $F = \overline{A}\overline{B}\overline{D} + \overline{A}BD + ABC\overline{D} + A\overline{B}CD$  using  $8 \times 1$  MUX and a NOT gate.

- (ii) Implement  $F = (A_0 \oplus A_2) + (A_1 \odot A_3)$  using only  $2 \times 1$  MUX circuits and basic inputs  $A_0$ ,  $A_1$ ,  $A_2$ ,  $A_3$ , 0 and 1.

[10 + 10 marks]

Page 61 of 71

Do not write in this margin

Page 62 of 71

Do not write in this margin

Page 63 of 71

Do not write in this margin

Q.8 (a)

A control system with unity negative feedback has an open loop transfer function,

$$G(s) = \frac{K}{s(s+1)(0.1s+1)}$$

and input,  $r(t) = 10tu(t)$ .

- Determine the steady state error  $(e_{ss})$  for K = 2.

- (ii) Find the minimum value of K for which,  $e_{ss} \le 0.1$  for a unit ramp input.

- (iii) For the value of K obtained in part (ii), obtain the closed loop transfer function of the system and thereby find the stability of system using R-H criteria.

$$ess = \frac{A}{Kv} = \frac{10}{2}$$

For Ramp input [11) KV= It SGH(S) = It K = (R) S-10 (S+1)1-(S+1) = (R)

$$ess = \frac{1}{k}$$

Ces Given ess

$$\leq 0.1$$

$$\frac{1}{k} \leq 0.1$$

$$\frac{1}{K} \leq 0$$

(iii)

$$G(S) = \frac{K}{S(S+1)(0.1S+1)}$$

$$GLD = 10$$

$S(S+1) (0.1S+1)$

$$CITF = \frac{10}{5(s+1)(0,xs+1)}$$

$$CITF = \frac{10}{S(S+1)(0,1S+1)}$$

$$1 + \frac{10}{S(S+1)(0,1S+1)}$$

$$CLTF T(S) = \frac{10}{S(S+1)(0,1S+1)}$$

$$CLTF T(S) = \frac{10}{S(S+1)(0,1S+1)}$$

$$T(S) = \frac{10}{(S^2 + S)(0.1S + 1) + 10}$$

$$= \frac{10}{0.1S^3 + S^2 + 0.1S^2 + S + 1}$$

$$= \frac{10}{0.103 + 0.2 + 0.15^2 + 5 + 10}$$

$$T(s) = \frac{10}{0.1s^2 + 1.1s^2 + s + 10}$$

for stability condution, - Using Rymethod

$$= \frac{01}{(1+21.0)(1+2)}$$

$$9(5) = S(5+1)(0.15+1) + 10 = 0$$

$9(5) = (S^2 + 5)(0.15+1) + 10 = 0$

$9(5) = (S^2 + 5)(0.15+1) + 10 = 0$

$$Q(S) = 0.1S^3 + 1.1S^2 + 1S + 10 = 0$$

Using R-H method.

So first column in the matrix is positive and having a same sign. so this system is stable. System.

Q.8(b)

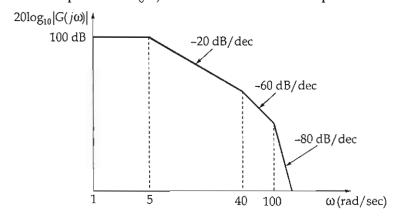

Define the terms: Minimum-phase system, Non-minimum phase system and all-pass system.

The magnitude plot of the open loop transfer function G(s) of a certain system is shown in the figure below:

- Determine G(s) if it is known that the system is of Minimum phase type.

- Estimate the phase of  $G(j\omega)$  at each of the corner frequencies.

[20 marks]

Minimum Phase System -?

If the system is said to be minimum phase System if the all poles and zero lies left side of s-plane is called minimum

phase system

example.

$$\frac{\text{K1S+1)}}{\text{(S42)(S+3)}}$$

Non minimum phone system -?

The system is socied to be Hon minimum phose system if Pither pole or zeros lies right half of 5- plane is called Non minimum phase system.

Example

$$GHISI = \frac{KIS-IJ}{State of}$$

Significant  $S-plane$ .

All pass System -: A system is said to All pair of pole zero pattern.

Example

TF=1-SRC

GIS) > determine (3)

from the Given Plot we can write.

GLS) = K.

$\left(\frac{S}{5}+1\right)\left(\frac{S}{40}+1\right)^2\left(\frac{S}{100}+1\right)^2$

to determin the value of K

M=-20xxxlogu +20logk W=1 M=100

$100 = 20 \log K$   $5 = \log K$   $K = 10^{5}$

put the value of 'k' in GIS) system

105.5 x402 ×100 (S+5) (S+40)2(S+100)

$G(S) = \frac{8 \times 10^8}{(5+5)(5+40)^2(5+100)}$

(ii)

$$\left[ \frac{G(j\omega)}{5} = -\tan^{-1} \left[ \frac{\omega}{5} \right] - 2\tan^{-1} \left[ \frac{\omega}{40} \right] - \tan^{-1} \left[ \frac{\omega}{100} \right] \right]$$

Corner frequery w= 5 reed ses

$$\angle G_{ij}(\omega) = -194.67^{\circ}$$

Q.8(c)

- (i) What are the Hazards that occur while designing a combinational circuit? Discuss different types of Hazards.

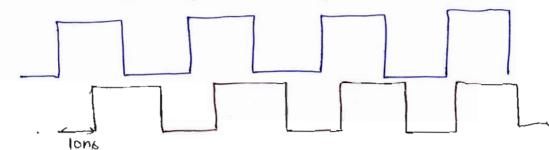

- (ii) Design a square wave generator of output frequency  $(f_s)$  using a single  $2 \times 1$  MUX circuit which suffers from a propagation delay of 10 ns. Also draw its output waveform and calculate the value of frequency  $(f_c)$ .

[10 + 10 marks]

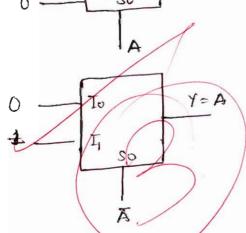

Square wave generator -: 11) Y = A

To

SO as simple Not leate will be able to produce a square wave generator

so we can replace the not hate with eximux as shown in the above. So we will be able to Goog Crenerate the Square wave output

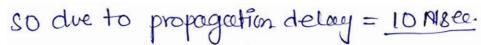

# SO Calculation offs -:

$$Tsq = 2x 1x 10$$

$$Tsq = 20nse$$

SO

$$f_s = \frac{1}{T_{sq}} = \frac{1}{20 \text{ mpc}} = \frac{50 \text{ mHz}}{50 \text{ mHz}}$$

## (i) Hazards -:

There are somony types of Hazords which are leads to answertented change in

the output.

Some time we wanted to some type of Hazards to make the circuit simple.

There are various types of Hazards presu

OStatic- o type

Detatic - 1 type

Blynamic type Morzards.

Static - 0 types - i this type of Hazends basically present in combination circuit. mesty. it will be due to as we get leng sequence of co. EXP- AND-OR.

Static-1 types -: 9+13 one type of Hazerds which Basically dominant in combinational crowit amich leads to change the endden output.

Dynamic Hazards -:

9t is one type of Hazerds which is present in Sequential crocuit, which Leads to sudden spikes in the clock signal or output signal. It is one of the Unwanted signal which may Leads to damage the crewit also Example