· Try to avoid

calculation

mistake

# **ESE 2025 : Mains Test Series**

UPSC ENGINEERING SERVICES EXAMINATION

# **Electrical Engineering**

**Test-5: Basic Electronics Engineering** + Computer Fundamentals + Electromagnetic Field Theory

| Name :       |           |             |                     |

|--------------|-----------|-------------|---------------------|

| Roll No :    |           |             |                     |

| Test Centres |           |             | Student's Signature |

| Delhi 🗇      | Bhopal 🗌  | Jaipur 🗌    |                     |

| Pune 🗌       | Kolkata 🗌 | Hyderabad 🗌 |                     |

#### **Instructions for Candidates**

- 1. Do furnish the appropriate details in the answer sheet (viz. Name & Roll No).

- 2. There are Eight questions divided in TWO sections.

- 3. Candidate has to attempt FIVE questions in all in English only.

- 4. Question no. 1 and 5 are compulsory and out of the remaining THREE are to be attempted choosing at least ONE question from each section.

- 5. Use only black/blue pen.

- 6. The space limit for every part of the question is specified in this Question Cum Answer Booklet. Candidate should write the answer in the space provided.

- 7. Any page or portion of the page left blank in the Question Cum Answer Booklet must be clearly struck off.

- 8. There are few rough work sheets at the end of this booklet. Strike off these pages after completion of the examination.

| FOR OFFICE USE          |                |  |

|-------------------------|----------------|--|

| Question No.            | Marks Obtained |  |

| Section                 | on-A           |  |

| Q.1                     | 41             |  |

| Q.2                     | 46             |  |

| Q.3                     |                |  |

| Q.4                     | 46             |  |

| Section                 | on-B           |  |

| Q.5                     | 39             |  |

| Q.6                     | 44             |  |

| Q.7                     |                |  |

| Q.8                     |                |  |

| Total Marks<br>Obtained | 216            |  |

Cross Checked by

Signature of Evaluator

Corp. office: 44 - A/1, Kalu Sarai, New Delhi-110016 | Ph: 9021300500 | Web: www.madeeasy.in

Read prostruction carefully

### **IMPORTANT INSTRUCTIONS**

CANDIDATES SHOULD READ THE UNDERMENTIONED INSTRUCTIONS CAREFULLY, VIOLATION OF ANY OF THE INSTRUCTIONS MAY LEAD TO PENALTY.

### **DONT'S**

- 1. Do not write your name or registration number anywhere inside this Question-cum-Answer Booklet (QCAB).

- 2. Do not write anything other than the actual answers to the questions anywhere inside your QCAB.

- 3. Do not tear off any leaves from your QCAB, if you find any page missing do not fail to notify the supervisor/invigilator.

- 4. Do not leave behind your QCAB on your table unattended, it should be handed over to the invigilator after conclusion of the exam.

#### DO'S

- 1. Read the Instructions on the cover page and strictly follow them.

- 2. Write your registration number and other particulars, in the space provided on the cover of QCAB.

- 3. Write legibly and neatly.

- 4. For rough notes or **calculation**, the last two blank pages of this booklet should be used. The rough notes should be crossed **through after**wards.

- 5. If you wish to cancel any work, draw your pen through it or write "Cancelled" across it, otherwise it may be evaluated.

- 6. Handover your QCAB personally to the invigilator before leaving the examination hall.

Q.1 (a)

# Section A : Basic Electronics Engineering + Computer Fundamentals + Electromagnetic Field Theory

If

$$\vec{J} = \frac{1}{r^3} (2\cos\theta \hat{a}_r + \sin\theta \hat{a}_\theta) A/m^2$$

, calculate the current passing through

- (i) a hemispherical shell of radius 20 cm,  $0 < \theta < \frac{\pi}{2}$ ,  $0 < \phi < 2\pi$ .

- (ii) a spherical shell of radius 10 cm.

$$J = \frac{1}{\gamma^3} \left( 2\cos\theta \, 9\hat{s} + \sin\theta \, 9\hat{o} \right) \, A/m^2 \quad [12 \, \text{marks}]$$

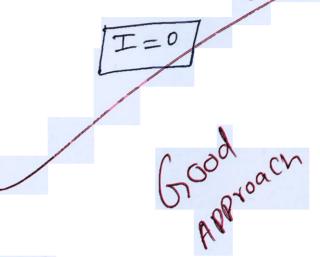

(i)

$$r = 20 \text{ cm}, 0 < 0 < \frac{\pi}{2}, 0 < \phi < 2\pi, \text{ Hernishherital}$$

$$I = \left( \int J \cdot dS \right)$$

$$I = \iint \frac{1}{\chi^3} \left( 2\cos\theta \, q\hat{s} + \sin\theta \, q\hat{b} \right) \cdot \chi^2 \sin\theta \, d\theta \, d\phi \, q\hat{s}$$

$$T = \iint \frac{1}{x^2} (2\cos\theta) \cdot x^2 \sin\theta \, d\theta \, d\phi$$

$$T = \iint \frac{2\pi}{x^2} \int_{0}^{\pi/2} \sin^2\theta \, d\theta \, d\phi$$

$$I = \frac{1}{\chi} \left( \cos 2\theta \right) \frac{1}{\chi_{L}} \times \left( \Phi \right) \frac{2\pi}{\sigma}$$

$$T = \frac{1}{20 \times 10^{-2} \times 2} 2 \times 2$$

$$I = 10x = 31.42 A$$

$$T = \frac{2}{7} \int_{0}^{\pi} \sin \theta \, d\theta \, d\phi$$

$$T = \frac{10}{7} \times 2\pi \left( \cos 2\theta \right)^{\circ}$$

$$T = 0$$

[12 marks]

Q.1 (b)

A charge distribution with spherical symmetry has density  $\rho_v = \begin{cases} \frac{\rho_0 r}{R}, & 0 \le r \le R \\ 0, & r > R \end{cases}$ .

Determine  $\vec{E}$  everywhere.

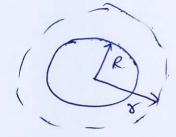

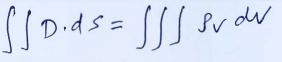

By Craus Law

In Spherical coordinates

$$\iint D_{\gamma} \cdot dS = \iiint_{Q} \frac{P_{Q} \times \chi^{2} \sin \theta}{R} d\tau d\theta d\rho$$

$$D_{8} \times 4\pi 8^{2} = \int_{R}^{8} \int_{0}^{3} d8 \times 4\pi$$

$$D_{8} = \frac{\beta_{0}}{\sqrt{2R}} \times \frac{3}{4} = D_{8} = \frac{\beta_{0} \times 2}{4R}$$

2)

8>R

SID.ds = SSS Sv dw Sv=e fee x>R D=0

Q.1 (c)

Consider a network connecting two systems located 3000 kilometers apart. The bandwidth of the network is 1.544 Mbps. The propagation speed of the media is  $0.16 \times 10^6$  km/sec. It is needed to design a Go-Back-N sliding window protocol for this network. The average frame size is 64 B. The network is to be used to its full capacity. Assume processing delays at nodes are negligible. Calculate the window size.

[12 marks]

MADE EASY Question Cum Answer Booklet

Page 6 of 79

Do not write in this marg Q.1 (d) What does "computer architecture" term means in regards to computing system? Enumerate properties of reduced instruction set computer architecture.

Computer Architecture is defined as the intercorrection of different components present in the computer organization. Computer Architecture basically has several parts connected together to do this specific tasks. Van Neuman architecture was the first Computer architecture where single memory was foresent. Properties of Reduced Instruction Set Computer Asch.

- 1) gt uses very less instruction set

- 2) 9t uns more registers

- 3) It requires less addressing modes

- Pipeling is successfull in RISC

- Cycli per Instruction i.e CPI = 1

- 6) gt uses hardwired control unit

- 7) Les flerible Control unt

- ex und in ARM processor.

Q.1 (e)

Determine the curl of the following vector fields:

- $\vec{A} = \rho z^2 \hat{\rho} + \rho \sin^2 \phi \hat{\phi} + 2\rho z \sin^2 \phi \hat{z}$ , in circular cylindrical coordinate system.

- (ii)  $\vec{B} = r\hat{r} + r\cos^2\theta\hat{\phi}$ , in spherical coordinate system.

(i)

$$A p = \int z^2 A \phi = \int \sin^2 \phi A z = 2 \int z \sin^2 \phi \left[ 6 + 6 \text{ marks} \right]$$

$$\frac{g_{n} \text{ aylindrical system}}{\sqrt{2}}$$

$$\frac{1}{\sqrt{2}} = \frac{1}{\sqrt{2}} = \frac{$$

=

$$\frac{1}{9} \left[ q_{9}^{2} \left( 2 \beta z \times 2 \cos \phi \sin \phi - 0 \right) - \beta q_{\phi}^{2} \left( 2 z \sin^{2} \phi - 2 \beta z \right) + q_{2}^{2} \left( 2 z \sin^{2} \phi - 0 \right) \right]$$

=

$$\sqrt{9 \cdot (2 \sin 24 \cdot z) \cdot 9} - (2 z \sin^2 4 - 2 z) \cdot 9} + 9z \sin^2 4 x z^3$$

$$\nabla XA = 2z\sin^2\phi q\hat{s} - 2z(\sin^2\phi - \beta)q\hat{\phi} + q\hat{z}\sin^2\phi$$

$$B_{8} = r \quad B_{0} = 0 \quad B_{4} = subset$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla x B = \frac{1}{r^{2} sin \theta} \quad \frac{\partial}{\partial x} \quad \frac{\partial}{\partial \theta} \quad \frac{\partial}{\partial \phi}$$

$$\nabla X D = \frac{1}{\sqrt{2} \sin \theta} \left[ a_{1}^{2} \left( \sqrt{2} \left( \cos^{3} \theta - 2 \cos \theta \sin^{2} \theta \right) \right) - \sqrt{2} a_{0}^{2} \left( 2 \sqrt{2} \sin \theta \cos^{2} \theta \right) \right] + a_{0}^{2} \left( \sqrt{2} \sqrt{2} \sin \theta \cos^{2} \theta \right)$$

$$\nabla X R = a_8^2 \left( \frac{\cos^3 \theta - 2 \cos \theta \sin^2 \theta}{\sin^2 \theta} \right) - 2a_0^2 \cos^2 \theta$$

$$\nabla XR = \left(\frac{\cos^3\theta}{\sin\theta} - 2\cos\theta\sin\theta\right)q_{\theta}^2 - 2\alpha\theta\cos\theta$$

Good

Q.2 (a)

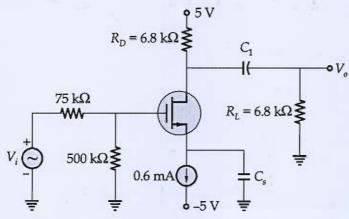

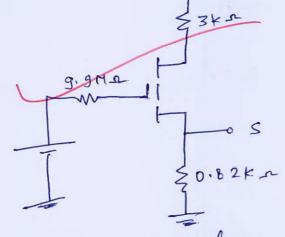

Determine the small signal voltage gain of the circuit shown in below figure having parameters  $V_T = 0.8 \text{ V}$ ,  $k = \frac{\mu_n C_{ox} W}{2L} = 1.2 \text{ mA/V}^2$ ,  $\lambda = 0$ . Also calculation gate-to-source voltage ( $V_{GSO}$ ).

DC Analysis -> All capacitors open & ac sources -coro [20 marks]

ID = 0.6 m A, MOFET is in saturation mode

Mow,

write in

this margi

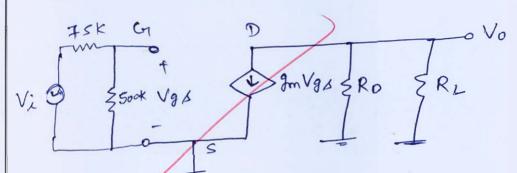

AC Analysis -> Drawing small signal model

Capacitos -> short circuited

desources -> off

From the above small signal model

from imput side

from Of D

$Av = V_0 = -g_m \times \frac{s_{00}}{s_{75}} \times (6.8|16.8k_a)$

to small signal voltage gain

Q.2 (b)

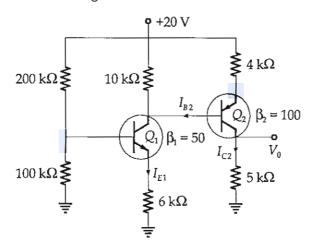

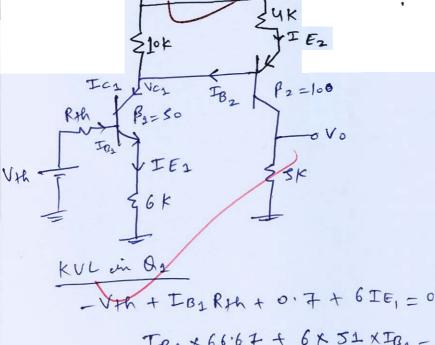

Consider the transistor configuration shown below.

### Determine:

- (i) Base current of transistor,  $Q_2$ .

- (ii) Collector current of transistor,  $Q_2$ .

- (iii) Emitter current of transistor,  $Q_1$ .

- (iv) Output voltage,  $V_0$ .

Applying therein equivalent at input/base of [20 marks]

Emitter Current Of Francistor Q2 IE1 = (2+P2) IB2 = 51 x 0016 TEI = 0.816 mA

Ic1 = IE1- FB1 = 0.8 mA

Again KVL in upper took

-20+4IE2+0.7+10(IB2-IC1)=0

4(1+P2) IR2+ 10 IB2-8=20-0.7

IB2 = 0.0659mA L) Base current of Q 2

Ica = P2 FOZ

Te2 = 6. 59 mA

Sollector current of Q2

10 = 5IG

Vo= 5x6.59

Vo = 32.94 Volts

Q.2(c)

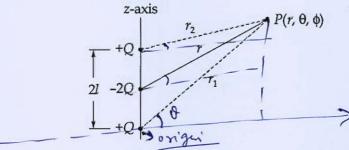

(i) Figure below shows a linear quadrupole arrangement, with charges +Q, -2Q and +Q disposed as indicated. Show that the potential due to this quadrupole at a large

distance 'r' in comparison with the spacing '2l' is  $V = \frac{Ql^2}{4\pi\epsilon_0 r^3} (3\cos^2\theta - 1)$ .

Assume the origin as shown in figure

+Q(0,0,0) gn cartesian

-QQ(0,0,1) system

$$VP = \frac{KQ}{Y_1} + \frac{K(-2Q)}{Y_2} + \frac{KQ}{Y_2} \rightarrow 0$$

$$\cos \theta = \sqrt{\gamma_1^2 - \sqrt{2}}$$

$$\cos\theta = \sqrt{r^2 - l^2} \rightarrow \bigcirc$$

$$\cos\theta = \sqrt{r^2 - l^2}$$

$$\cos\theta = \sqrt{r^2 - l^2}$$

$$\cos\theta = \sqrt{r^2 - l^2}$$

x2 UB20=82-12

**\*\*\***

$$3\cos^2 0 - 1 = \frac{3r^2 - 3\ell^2}{r^2} - 1$$

$$= -\frac{2\ell^2}{8^2} \rightarrow \text{using this}$$

$$V \text{ formula}$$

$$V = \frac{12}{8} \left( 360^{2} \theta^{-1} \right)$$

$$V = \frac{8 l^2}{4 \pi^2 \sqrt{3 (3 (3 + 0)^2)}}$$

(100 d

Q.2 (c)

(ii) Region  $y \le 0$  consists of a perfect conductor while  $y \ge 0$  is a dielectric medium ( $\varepsilon_r = 2$ ). If there is a surface charge of 2 nC/m<sup>2</sup> on the conductor, determine  $\vec{E}$  and  $\vec{D}$  at A(3, -2, 2) and B(-4, 1, 5).

$$\int S = 2 n \frac{c}{m^2}$$

$$2x = 2$$

$$3 > 0$$

[8 marks]

$$2x = 2$$

$$4 + 0 = 2$$

$$3 > 0$$

$$2x = 1$$

$$3 < 0$$

$$3 < 0$$

$$3 < 0$$

$$3 < 0$$

$$3 < 0$$

$$\overrightarrow{D} = S_{5} = 2nc/m^{2} \overrightarrow{ay}$$

$$E = \frac{D}{\varepsilon_{0}} = \frac{2 \times 10^{-9}}{\varepsilon_{0}} = \frac{2 \times 10^{-9}}{8.854 \times 10^{-12}}$$

$$[E = 225.88 \frac{\text{agV/m}}{\text{J}}]$$

y=1 means [4 >0/

Good

Do not write in this margin

Q.3 (a)

Two extensive homogeneous isotropic dielectric meet on plane z=0. For z>0,  $\varepsilon_{r1}=4$  and for z<0,  $\varepsilon_{r2}=3$ . A uniform electric field  $\vec{E}_1=5\hat{a}_x-2\hat{a}_y+3\hat{a}_z$  kV/m exists for  $z\geq0$ .

Find:

- (i)  $\vec{E}_2$  for  $z \le 0$ .

- (ii) The angles  $\vec{E}_1$  and  $\vec{E}_2$  make with the interface.

- (iii) The energy densities (in  $J/m^3$ ) in both dielectrics.

- (iv) The energy within a cube of side 2 m centered at (3, 4, -5).

[20 marks]

# MADE EASY Question Cum Answer Booklet

Page 23 of 79

Do not write in this margin

Q.3 (b)

A solid conductor of circular cross-section with a radius of 5 mm has a conductivity that varies with radius, the conductor is 20 m long and there is a potential difference of 0.1 V dc between its two ends. Within the conductor  $\vec{H}=10^5\rho^2\hat{a}_{\phi}$  A/m.

- (i) Find conductivity  $\sigma$ .

- (ii) Determine the resistance between the two ends.

[20 marks]

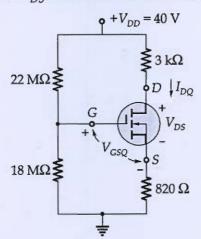

Q.4 (a)

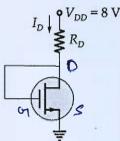

Determine  $I_{DQ}$  ,  $V_{GS\,Q}$  and  $V_{DS}$  for the circuit shown in figure,

$V_{GS \text{ (Th)}} = 5 \text{ V}, I_D(\text{on}) = 3 \text{ mA at } V_{GS}(\text{on}) = 10 \text{ V}.$

[20 marks]

Applying therein equivalent at input of gate

$$R_{th} = \frac{18 \times 22}{18 + 22} = 9.9 M \Omega$$

18 V

From the given values

V\_th = SV To = 3 mA Voy s = 10 V

$$T_0 = T_{OSS} \left( 1 - \frac{V_{OSS}}{V_{t}} \right)^2$$

$$3 = Ioss \left(1 - \frac{10}{5}\right)^2$$

Now, from the circuit drawn  $V_{CY} = 18V$   $V_{S} = 0.82 Jp$

Vars = 18-0.82 To

To = Toss (1- Vors)2

$T_0 = 3\left(1 - \frac{18 - 0.82 T_0}{5}\right)^2$

$\frac{2550}{3} = (5 - 18 + 0.8250)^2$

25 ID = (0.82 ID-13)2

0.672 To +169-21.32 To = 25 To

0.672 In 2 - 4632 In +169=0

ID = 3.86 m A

VOIS= 18-0.82 x 3.86

Vas= 14.83 V

Now, KVL

-40+3ID + VDS+ 0.82 ID=0

VDS= 40- 3.8250

Vos= 40-3.82 x 2.86

Vos=25.25V

- Q.4 (b)

- (i) Write a program in C language to sort the array of numbers in ascending order using bubble sort.

- (ii) Explain briefly the terms: Translator software, assembler, compiler and interpreter. Differentiate between a compiler and an interpreter.

[10 + 10 marks]

(i) Sorting the array using bubble sort

int < state : 1);

int < state : 1);

for (i = a, i < n - 1, i + +);

for (j = 0, j < n - 1 - i, j + +);

for (j = 0, j < n - 1 - i, j + +);

femp = a(i);

a(j) = a(j+1);

a(j+1) = +emp,

y

C Program

int < stdio.h>

int < corio.h>

int < corio.h>

int < math.h>

int main ();

int i, j, temp, n;

int a[n];

Printf(" load the array",);

Scanf(" lod", f n);

For (i=o, i < n-1, i+t);

for (j=o, j < jn-1-i, j+t);

L if a[j] > a[j+1];

temp ==a[j+i];

a[j+i] == temp;

y

break

(ii) Assembler > Assembler is used to consect assembly language program into machine language cody that processor can understand.

Compiler > In computing, a compiler is a computer brogram that translates computer code written in one programming language into another language.

(High level)

Interpreter > Interpreter also used in computer bogsoams to translate the computer code from one language to other and then execute the program.

Translator Software > I this tool is used to franslate the language from one form to other.

code line by line.

Difference between Compiler of Interpreter

Both Compiler and soft Interpreter do the same job of translating the high level language into grachine understandable language flowever they both differ in approach performance of that translation.

Compiler translates the entire program into machine understandable code at once while Interpreter translates of also executes the

- Q.4 (c)

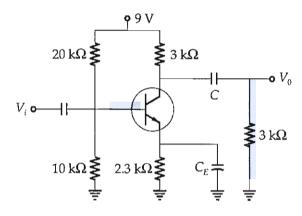

- (i) In the following transistor circuit,  $V_{BE}$  = 0.7 V,  $V_{T}$  = 25 mV and the capacitance are very large.

#### Find:

- **1.** The value of DC current  $I_F$ .

- 2. The mid band voltage gain of the amplifier.

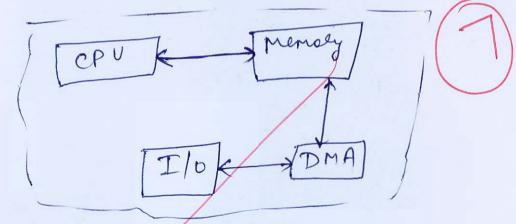

- (ii) What is meant by Direct Memory Access (DMA)? Explain briefly different types of DMA transfer modes.

[12 + 8 marks]

(i) DC Analysis

Capacitor > open

AC sources > shorted

1

$\frac{3}{3} \times \frac{10}{30}$   $\frac{7}{3} \times \frac{10}{30}$

KVL V+h + IBR+h +0: 7 + 2:3 IF = 0 ASsuming [B=\infty] Fa=0

Z-3

IE = 1 mA

Mid band holtage gain

gm = Ic = 1 = 0.04 m A/V

Capacitor > shorted dc. sowers > off

Small Signal model

Vi B ZRH ZXX VX I Janva Zxx Z3xn

Vo = - gm Vx (3 kx // 3 kx)

$A_{V} = \frac{V_{0}}{V_{i}} = \frac{V_{0}}{V_{K}} = -\frac{g_{m}(1.5 + n)}{V_{K}}$   $A_{V} = \frac{1}{2.5} \times 1.5 \quad \text{M.C.}$

Av=-0.06 /

# (ii) Direct Memory Access (DMA)

Direct Memory access is the easiest and fastest way to make possible the data transfer between I/O device and memory. With the help of DMA, data is transferred from memory to I/B Ox vice versa. Unlike other processes, DMA is much faster and reliable process.

DMA utilizes the internal buses of processor in doing the operation. CPV meanwhile during that time Keeps on doing the does which doesn't require the use of buses

Modes of data transfer

- 1) Block transfer mode > In this mode, a block of data is keep on transfering from I/o derive to memory or vice verse.

- 2) Joter leaved mode >

- 3) Cycle stealing mode > It is the fastest mode where data is transferred in one cycle

[12 marks]

#### Section B : Basic Electronics Engineering + Computer Fundamentals + Electromagnetic Field Theory

Q.5 (a) The xy-plane serves as the interface between two different mediums. Medium-1 (z < 0) is filled with a material whose  $\mu_r = 6$  and medium-2 (z > 0) is filled with a material

whose  $\mu_r = 4$ . If the interface carries current  $\left(\frac{1}{\mu_0}\right)\hat{a}_y$  mA/m and  $\vec{B}_2 = 5\hat{a}_x + 8\hat{a}_z$  mWb/m<sup>2</sup>,

find  $\vec{H}_1$  and  $\vec{B}_1$ .

$$T = \frac{1}{40}$$

ay  $\frac{1}{100}$   $\frac{1}{100}$

Ban Baz

Since, normal component of B is continuous

$$\overrightarrow{B_{2n}} = \overrightarrow{B_{2n}} = 89^{2} \rightarrow 3$$

Now !

$$\overrightarrow{H}_{1+} - \overrightarrow{H}_{2+} = (\mathring{x} \times \mathring{n})$$

$$\overrightarrow{H}_{1+} - \overrightarrow{H}_{2+} = \underbrace{\underbrace{\underbrace{A_0}}_{M_0} (a_0^2 \times a_2^2)}$$

from 1 f 1

$$\frac{1}{114} = \frac{5}{440} + \frac{1}{40} \cdot \frac{1}{40} \cdot \frac{1}{40}$$

$$\frac{1}{114} = \frac{9}{440} \cdot \frac{9}{110}$$

$$M_1 = \frac{9}{4} \frac{9n^2 + \frac{4}{3} \frac{9n^2}{3}}{340}$$

$$11 = \frac{1}{40} \left( \frac{9}{4} \frac{9}{4} + \frac{4}{3} \frac{9}{2} \right) m H/m$$

$$B_1 = B_1 + k_{2m}$$

$$B_1 = 9 + a_m^2 + 892 m wb/m^2$$

$V = \frac{-8^2}{9^2(r^2+9^2)}$

Q.5 (b)

In spherical coordinates, electric field intensity is given by  $\vec{E} = \frac{2r}{(r^2 + a^2)^2} \hat{a}_r \text{ V/m.}$  Find the potential at any point, using the reference

- (i) V = 0 at infinity.

- (ii) V = 0 at r = 0.

- (iii) V = 100 at r = a.

Civen,

$$E = \frac{2r}{(r^2 + q^2)^2} q_r^2 \frac{1}{\sqrt{m}}$$

$V = -\int E \cdot dl = -\int \frac{2r}{(r^2 + q^2)^2} dr$

$V = -\int \frac{dr}{r^2 + q^2} = \frac{1}{r} = \frac{1}{(r^2 + q^2)} f(r)$

$V = \int \frac{1}{r^2 + q^2} + C$

$V = \int \frac{1}{r^2 + q^2} + C$

$$100 = \frac{1}{x^2 + 9^2} + C$$

$$C = 100 - \frac{1}{292}$$

Q.5 (c)

Consider a two level memory hierarchy,  $L_1$  (cache) has an accessing time of 5 ns and main memory has an accessing time of 100 ns. Writing or updating contents takes 20 ns and 200 ns for  $L_1$  and main memory respectively. Assume  $L_1$  gives misses 20% of the time with 60% of the instructions are read only instructions. What is the average access time for system (in ns) if it uses WRITE-THROUGH technique?

Given, two level memory hierarchy

L1 > tc1 = 5ns tm2 = 100ns

200ns

For read only instruction

for read only instruction

H=0.6

tang =  $0.6 \times 5 + 0.4 \times 100$

tang = 430A

Now, by using WRITE-THROUGH technique tang. = 0.8 × (43 +20) = + 0.2 × (100+200)

given tang = 50.4 + 60

301. hit

tang = No.4 ns

Q.5 (d)

In the circuit shown,  $V_T$  is 1 V. When  $R_D$  is 3 k $\Omega$  then  $I_D$  is 2 mA and when  $R_D$  decreased by 1 kΩ then find the value of  $I_D$ .

Given, VT = 1V Ro = 3kr ID = 2mA [12 marks] RD=2K& Io=?

$$2 = \frac{8 - v_{0s}}{3} \Rightarrow v_{0s} = 2v$$

$$T_0 = \frac{8-2}{2}$$

$$T_0 = \frac{8 - 2}{2}$$

$$T_0 = 3 \text{ mA}$$

Do not write in this margin Q.5 (e) What are the basic functions of an operating system?

Operating system is a large conflin software used to functions given below -

- 1) File management > a) Managing the file and directories

- b) Deleting the corrupt files

- c) controlling the file storage.

- 2) <u>Device Management</u> -> managing the device driver

- 3) Mendy management > a) allocation of optimum memory

- b) Preventing fragmentation

- 4) Projection of Security > 9) Projection of data

- b) Authentication of programs & data

- 5) User griteface > Providing an interface between Computer network & computer user.

protection

getwits

Operating

Operating

Price management

Premagement

Premageme

Q.6 (a)

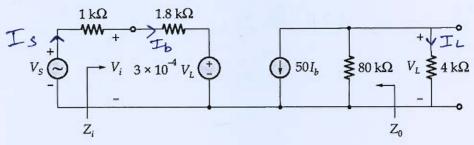

The small signal h-parameter ac equivalent circuit of a certain transistor connected in CE configuration is as shown in figure below.

#### Calculate:

- (i) Current gain.

- (ii) Voltage gain  $\frac{V_L}{V_c}$ .

- (iii) Input impedance  $Z_{in}$ .

- (iv) Output impedance Z<sub>out</sub>.

[20 marks]

From the given small signal h-parameter model

$$AI = \frac{IL}{I_S} = \frac{IL}{I_b} = -47.62$$

$$A_{V} = \frac{V_{L}}{V_{S}}$$

$$V_{L} = -50 \text{ Jb} \times \left(\frac{80 \times 4}{84}\right)$$

from i/b loop

KVL

from O fo

$$Av = \frac{VL}{VS} = \frac{-190.47 + Fb}{2.74 + Fb}$$

(iii) grønt großedance (Zin)

from equation (2) Vs = 2. 7/4 Ib

(IV) Outfut Impedance (Zout), Zout = Vo

Vs = 0

15075380K 34K 7 V.

FronkVL 2.876 = - 3×10-4 VL

$$\frac{816 = -3 \times 10^{-4} \text{ Vg}}{2.9} \rightarrow 3$$

$$Z_{in} = \frac{V_{i}}{I_{b}} = \frac{1.8 \div 3 \times 10^{-4} \times 190.47}{1}$$

36 Zin is asked before source

- 2.6 (b)

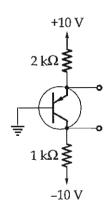

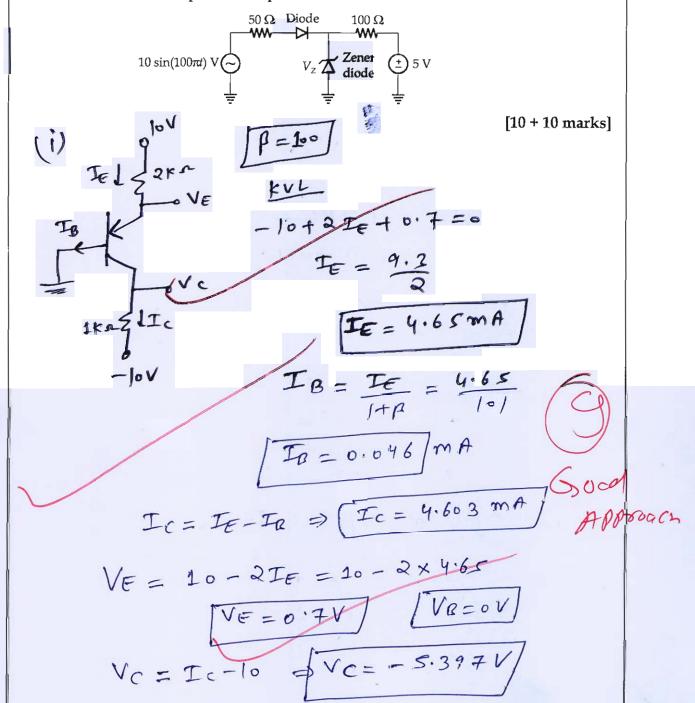

- (i) Determine the voltages at all nodes and currents through all branches. (Assume  $\beta = 100$ ).

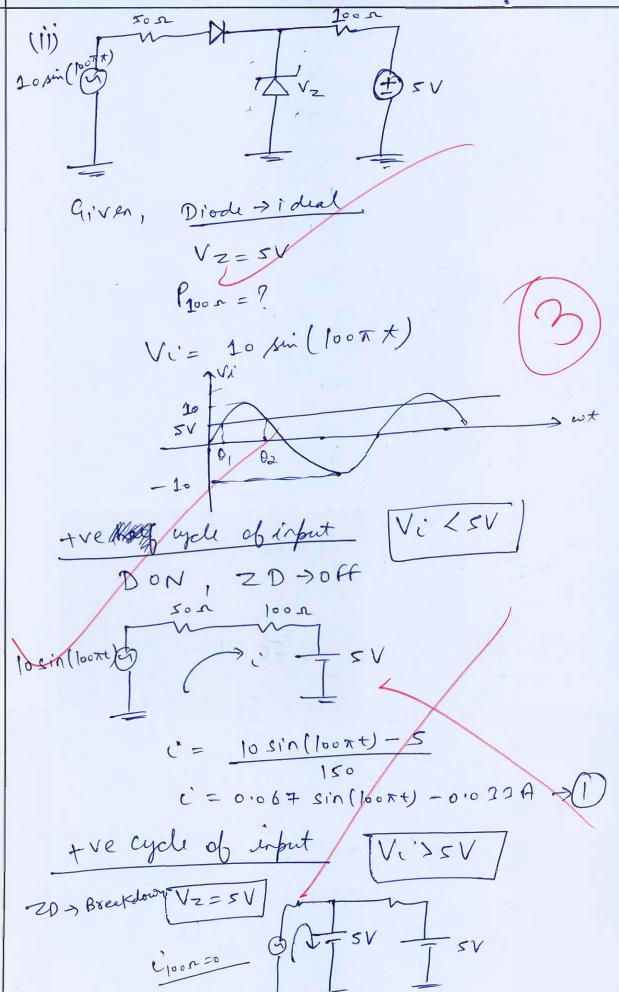

(ii) If the diodes in the circuit shown are ideal and the breakdown voltage  $V_z$  of the zener diode is 5 V, find the power dissipated in the 100  $\Omega$  resistor.

ve apple of input DOFF ZD -> ON (FB)

DOFF

$$ZD \to DN (FB)$$

$$\frac{100 \text{ } 12}{1} \text{ } 5V$$

$$\frac{1}{1} \text{ } 5V$$

$$P_2 = i^2 \times 100$$

$$P_2 = (0.05)^2 \times 100$$

$$P_3 = 0.25W \rightarrow (2.00)$$

$$\int_{2}^{2} = (0.05)^{2} \times 100$$

$$\int_{2}^{2} = 0.25W \rightarrow 2$$

$$\lim_{N \to \infty} = \left[\frac{1}{T} \int_{0.0675}^{0} (0.0675) - 0.032\right]^{2} dt$$

$$\int_{1}^{2} = 0.25W \rightarrow 2$$

$$\lim_{N \to \infty} = \left[\frac{1}{T} \int_{0}^{1} (0.0675) - 0.032\right]^{2} dt$$

$$\int_{0}^{2} = 30$$

$$0_1 = 3in^{-1} = 3.$$

$0_2 = 15.$

## E E□S앀 Question Cum Answer Booklet

- Q.6 (c) (i) Explain the IEEE standard 754 floating point numbers representation.

- (ii) Determine the size of subfields (in bits) in the address for direct mapping and associative mapping cache scheme:

Size of main memory = 256 MB

Size of cache memory = 1 MB

The address space of this processor is 256 MB. The block size is 128 bytes.

[10 + 10 marks]

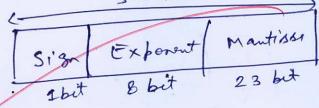

(i) IEEE Standard 754 floating point no representation

It is a method of representing any number unto a way easy form to understant and emplement. This representation helps in executing & Calculating very complex problems. This IEEE standard savus time, quite reliable. There are three terms included in it

1) Sign bit > Sign bit is used to tell about the whether the number written is positive or regative.

0 -> tre number 1 -> -ve rumber

2) Exponent -> place, the actual exponent is converted into Stored exponent with the help of bias.

entral ( et bias = E f) stored emponent emponent

3) Martiste -> Martiste is the magnifude represented in the form of 0 and 1. The representation of martiple is in two ways inflict & explicit

representation. It is represented after decimal as M and before decimal a 1 is taken.

IFEE754 Standard

1) Single procision 32-bit

2) Double Pricipion

Sign Exponent mantiska 1 bit 12 bit 52 bit

(ii) Given

Size of MM = 256MB = 28 bits

Size of CM = 1MB = 20 bits

Block size = 128 by tes = 7 bits

Associative mapping

Total processor space = 28 bits

Tag space = 28 - 7 = 21 bits

Tag Word

## Direct Mapping

No of Cache lines =  $\frac{1MR}{128 \text{ byter}} = \frac{2^{20}}{2^{7}} = 2^{13}$

No of word | blocks = 7

8 bits 13 bits 7 bits

Jag = 28 - (12+7) = 8 bits

2.7 (a)

value of N.

#### MADE EASY Question Cum Answer Booklet

Page 59 of 79

Do not write in this margin

(i) A processor has 16 integer registers (R0, R1, ....., R15) and 64 floating point registers (F0, F1, ....., F63). It uses a 2-byte instruction format. There are four categories of instructions: Type-1, Type-2, Type-3 and Type-4. Type-1 category consists of four instructions, each with 3 integer register operands (3Rs). Type-2 category consists of eight instructions, each with 2 floating point register operands (2Fs). Type-3 category consists of fourteen instructions, each with one integer register operand and one floating point register operand (1R+1F). Type-4 category consists of N instructions, each with a floating point register operand (IF). Find the maximum

[12 marks]

.7 (a)

## **MADE EASY** Question Cum Answer Booklet

Page 61 of 79

Do not write in this margin

(ii) The memory access time is 1 nanosecond for a read operation with a hit in cache, 5 nanoseconds for a read operation with a miss in cache, 2 nanoseconds for a write operation with a hit in cache and 10 nanoseconds for a write operation with a miss in cache. Execution of a sequence of instructions involves 100 instruction fetch operations, 60 memory operand read operations and 40 memory operand write operations. The cache hit-ratio is 0.9. Find the average memory access time (in nanoseconds) in executing the sequence of instructions.

[8 marks]

MADE EASY Question Cum Answer Booklet

Page 62 of 79

write in this mar

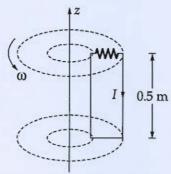

- Q.7 (c)

- (i) A rectangular conducting loop with resistance of  $0.2~\Omega$  rotates at 500 rpm, as shown in figure below. The vertical conductor at  $r_1=0.03$  m is in the field  $\vec{B}_1=0.25\hat{a}_rT$  and other conductor is at  $r_2=0.05$  m and is in the field  $\vec{B}_2=0.8\hat{a}_rT$ . Find the current flowing in the loop.

(ii) A wire of non-magnetic material with radius *R* and length *l* carries a current *I*, which is uniformly distributed over its cross-section. What is the magnetic energy inside the wire?

[14 + 6 marks]

|    |                                       |   |               | •                                 |

|----|---------------------------------------|---|---------------|-----------------------------------|

| EE | MADE EASY Question Cum Answer Booklet | 1 | Page 69 of 79 | Do not<br>write in<br>this margin |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

|    |                                       |   |               |                                   |

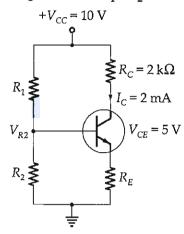

Q.8 (a)

A silicon n-p-n transistor operated with self bias gives  $V_{CEQ}$  = 5 V,  $I_{CQ}$  = 2 mA for  $V_{CC}$  = 10 V and  $R_C$  = 2 K. If  $\beta$  for the transistor is 50,  $V_{BE}$  = 0.7 V and stability factor "S" is 5 calculate, the values of biasing resistors  $R_1$ ,  $R_2$  and  $R_E$ .

[20 marks]

| MADE | ERSY | Question Cum A | Answer Booklet |  | Page 71 of 79 | Do not<br>write in<br>this margin |

|------|------|----------------|----------------|--|---------------|-----------------------------------|

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

|      |      |                |                |  |               |                                   |

8 (b)

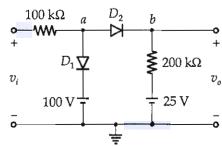

Determine and sketch the voltage transfer characteristic of the circuit shown in the figure below.

(Assume that the diodes are ideal)

[20 marks]

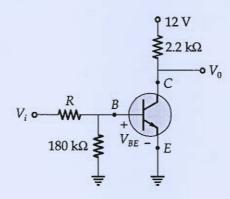

Q.8 (c) In the circuit shown below, a silicon transistor with specifications:  $\beta \ge 30$  and  $I_{CBO} = 100$  nA.

## Determine:

- (i) The value of  $V_0$  for  $V_i$  = 12 V and R = 20 k $\Omega$  and show that transistor is in saturation.

- (ii) The minimum value of R for the transistor to remain in the active region for  $V_i = 12 \text{ V}$ .

- (iii) The value of  $V_0$  for  $V_i$  = 1 V and R = 15 k $\Omega$ , also find the region of operation.

[20 marks]

| E | MADE | ERSY | Question Cum | Answer Booklet | I | Page 77 of 79 | Do not<br>write in<br>this margin |

|---|------|------|--------------|----------------|---|---------------|-----------------------------------|

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

|   |      |      |              |                |   |               |                                   |

| E | MADE EASY Question Cum Answer Booklet Page 79 of 79 | Do not<br>write in<br>this margin |

|---|-----------------------------------------------------|-----------------------------------|

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   |                                                     |                                   |

|   | 0000                                                |                                   |

|   |                                                     |                                   |