# **Detailed Solutions**

# ESE-2025 Mains Test Series

# E & T Engineering Test No: 2

# Section A : Digital Circuits + Signals and Systems + Microprocessors & Microcontroller

# Q.1 (a) Solution:

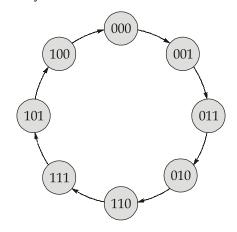

The state diagram for the 3-bit binary counter.

The state table for 3-bit binary counter,

| Pre   | sent s | tate  | N       | Next state      |                              |  |  |  |  |

|-------|--------|-------|---------|-----------------|------------------------------|--|--|--|--|

| $Q_2$ | $Q_1$  | $Q_0$ | $Q_2^+$ | $Q_1^{\dagger}$ | $Q_0^{\scriptscriptstyle +}$ |  |  |  |  |

| 0     | 0      | 0     | 0       | 0               | 1                            |  |  |  |  |

| 0     | 0      | 1     | 0       | 1               | 0                            |  |  |  |  |

| 0     | 1      | 0     | 0       | 1               | 1                            |  |  |  |  |

| 0     | 1      | 1     | 1       | 0               | 0                            |  |  |  |  |

| 1     | 0      | 0     | 1       | 0               | 1                            |  |  |  |  |

| 1     | 0      | 1     | 1       | 1               | 0                            |  |  |  |  |

| 1     | 1      | 0     | 1       | 1               | 1                            |  |  |  |  |

| 1     | 1      | 1     | 0       | 0               | 0                            |  |  |  |  |

The excitation table:

#### **Output state transitions**

| Pre   | sent s | tate  | N         | lext sta                     | Flip f                       | Flip flop inputs |       |       |  |

|-------|--------|-------|-----------|------------------------------|------------------------------|------------------|-------|-------|--|

| $Q_2$ | $Q_1$  | $Q_0$ | $Q_2^{+}$ | $Q_1^{\scriptscriptstyle +}$ | $Q_0^{\scriptscriptstyle +}$ | $T_2$            | $T_1$ | $T_0$ |  |

| 0     | 0      | 0     | 0         | 0                            | 1                            | 0                | 0     | 1     |  |

| 0     | 0      | 1     | 0         | 1                            | 0                            | 0                | 1     | 1     |  |

| 0     | 1      | 0     | 0         | 1                            | 1                            | 0                | 0     | 1     |  |

| 0     | 1      | 1     | 1         | 0                            | 0                            | 1                | 1     | 1     |  |

| 1     | 0      | 0     | 1         | 0                            | 1                            | 0                | 0     | 1     |  |

| 1     | 0      | 1     | 1         | 1                            | 0                            | 0                | 1     | 1     |  |

| 1     | 1      | 0     | 1         | 1                            | 1                            | 0                | 0     | 1     |  |

| 1     | 1      | 1     | 0         | 0                            | 0                            | 1                | 1     | 1     |  |

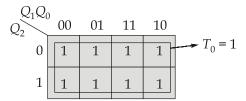

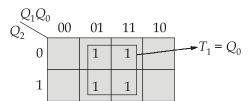

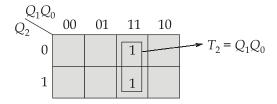

The Boolean expressions for flip-flop inputs  $T_{2^\prime}$   $T_1$  and  $T_0$  as

For  $T_0$ :

For  $T_1$ :

For  $T_2$ :

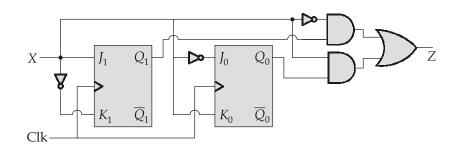

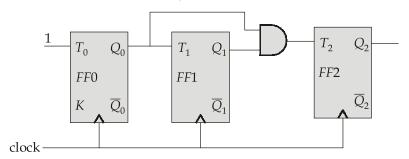

The logic diagram, since it is 3-bit binary counter we need 3FFs.

# Q.1 (b) Solution:

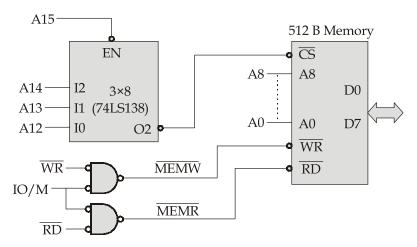

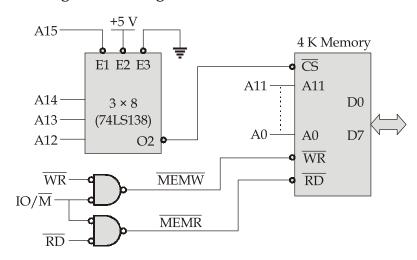

(i) 8085 Microprocessor has 16 address lines A0-A15. For interfacing 512 bytes i.e. 29 bytes/address locations, 9 address lines are required. So A0-A8 can be used to directly connect to address bus of memory.

From the remaining address lines A9-A15, three address lines A15-A12 can be used as enable and input lines to  $3 \times 8$  decoder for generating a chip select signal to memory as shown below. We assume the chip is selected i.e.  $\overline{CS} = 0$  when the inputs to the decoder A15 = 0, A14 = 0, A13 = 0 and A12 = 0. A11-A9 can be considered as don't care signals. Thus, the memory address map is given by,

| A15 | A14 | A13 | A12 | A11 | A10 | <b>A9</b> | <b>A</b> 8 | <b>A</b> 7 | <b>A6</b> | <b>A5</b> | <b>A4</b> | <b>A3</b> | A2 | <b>A1</b> | A0 |

|-----|-----|-----|-----|-----|-----|-----------|------------|------------|-----------|-----------|-----------|-----------|----|-----------|----|

| 0   | 0   | 0   | 0   | Χ   | Χ   | X         | 0          | 0          | 0         | 0         | 0         | 0         | 0  | 0         | 0  |

| 0   | 0   | 0   | 0   | Χ   | Х   | X         | 1          | 1          | 1         | 1         | 1         | 1         | 1  | 1         | 1  |

Because of the don't care signals, the address range can be

0000 to 01FF

0200 to 03FF

0400 to 05FF

0600 to 07FF

0800 to 09FF

0A00 to 0BFF

0C00 to 0DFF

0E00 to 0FFF

#### Address decoding circuit:

Address decoding circuit using 3 × 8 decoder

(ii) The 8085 assembly language program to move a block of data of 16 bytes starting from address location 2050H to another location starting from 2070H is given as below:

#### Instruction

LXI H, 2050H; Load starting address of the block into register pair HL

LXI D, 2070H; Load destination address into register pair DE

LXI B, 10H; Load counter (number of bytes to move i.e.  $16_{10} = 10H$ ) into

register pair BC

L1: MOV A, M; Move data from source address pointed by HL to

accumulator A

STAXD; Move data from accumulator A to destination address

pointed by DE

INX H; Increment source address

INX D; Increment destination address

DCX B; Decrement counter

JNZ L1; Jump to L1 if counter is not zero

HLT; Halt the program

# Q.1 (c) Solution:

$X[0] \bullet$ 1/8 x[0](i)  $X[4] \bullet$  $W_8^{-0}$  1/8 x[1]1/8 x[2] $X[2] \bullet$  $W_8^{-0}$  $W_8^{-0}$  1/8 x[3]X[6] • 1/8 x[4] $X[1] \bullet$  $W_{8}^{-0}$  $W_8^{-0}$  1/8 x[5] $X[5] \bullet$  $W_8^{-1}$ X[3]1/8 x[6] $W_8^{-0}$  1/8 x[7]

Test No: 2

**Statement:** If x[n] is causal [i.e., x[n] = 0 for n < 0], then  $x[0] = \lim_{n \to \infty} X(z)$

Proof: By definition of z-transform, we have

$$X(z) = \sum_{n=-\infty}^{+\infty} x[n] z^{-n}$$

Since x[n] = 0 for n < 0, we obtain

$$X(z) = \sum_{n=0}^{\infty} x[n] z^{-n}$$

$$X(z) = x[0] + x[1]z^{-1} + x[2]z^{-2} + x[3]z^{-3} + \dots$$

$$\Rightarrow \lim_{z \to \infty} X(z) = \lim_{z \to \infty} \left[ x[0] + x[1]z^{-1} + x[2]z^{-2} + x[3]z^{-3} + \dots \right]$$

$$\Rightarrow \lim_{z \to \infty} X(z) = x[0]$$

# Q.1 (d) Solution:

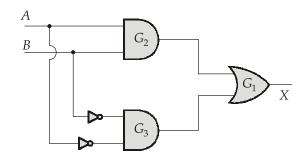

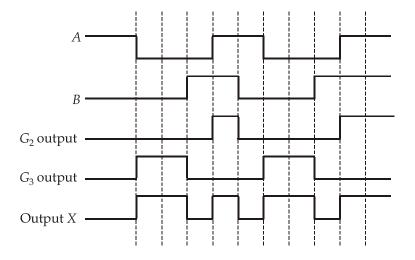

(i) Given logic circuit,

Output,

$$X = AB + \overline{A}\overline{B} = A \odot B$$

When both inputs are high or low, the output *X* is HIGH.

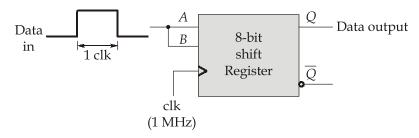

(ii) Given, serial-in-serial-out shift register,

When the given input pulse applied to the serial input, it enters the first stage on the triggering edge of the clock pulse.

It then shifted from stage to stage on each successive clock pulse until it appears on serial output n clock periods.

Given, clock frequency,  $f_{\rm clk}$  = 1 MHz the time period of clock,

$$T_{\text{clk}} = \frac{1}{f_{clk}} = 1 \,\mu \,\text{sec}$$

For n-bit serial-in-serial-out shift register,

the time delay for output is  $n \times T_{\text{clk}}$

$$t_d = 8 \times 1 = 8 \,\mu\text{sec}$$

# Q.1 (e) Solution:

(i) Given,

$$y(t) = e^{-2t}u(t)$$

System function,  $H(s) = \frac{Y(s)}{X(s)} = \frac{s-1}{s+1}$

By taking Laplace transform of y(t),

$$Y(s) = \frac{1}{s+2}; \text{Re}\{s\} > -2$$

$$X(s) = \frac{Y(s)}{H(s)} = \frac{\frac{1}{s+2}}{\frac{s-1}{s+1}}$$

$$X(s) = \frac{s+1}{(s-1)(s+2)}$$

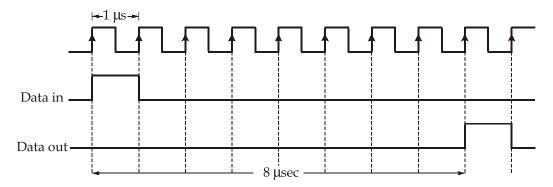

The pole-zero diagram of X(s) is

Since the given system is a causal system, the ROC of the impulse response is right-sided. Thus, from the given H(s), the ROC is Re $\{s\} > -1$ . We know that the ROC of Y(s) is at least the intersection of the ROCs of X(s) and Y(s).

In the above case, we can choose the ROC of X(s) to be either  $-2 < Re\{s\} < 1$  (or)  $Re\{s\} > 1$ .

In both cases, we get the same ROC for Y(s) because the poles at s = -1 and s = 1 in H(s) and X(s) respectively are cancelled out by zeros.

The partial fraction expansion of X(s) is

$$X(s) = \frac{\frac{2}{3}}{s-1} + \frac{\frac{1}{3}}{s+2}$$

$\therefore$  Taking the ROC of X(s) to be  $-2 < \text{Re}\{s\} < 1$

We get,

$$x(t) = \frac{2}{3}e^{t}\left\{-u(-t)\right\} + \frac{1}{3}e^{-2t}u(t)$$

Taking the ROC of X(s) to be Re $\{s\} > 1$ , we get

$$x(t) = \frac{2}{3}e^{t}u(t) + \frac{1}{3}e^{-2t}u(t)$$

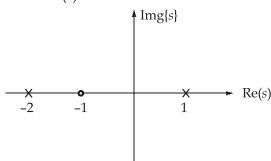

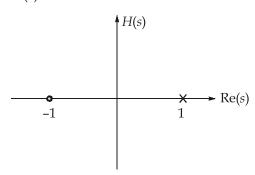

(ii) From the given information, we can write

$$H(s)Y(s) = X(s)$$

(Here, X(s) is the output and Y(s) is the input)

Clearly,

$$H(s) = \frac{X(s)}{Y(s)} = \frac{s+1}{s-1}$$

MADE ERSY

The pole-zero plot of H(s) is

Since the system is given to be stable, the ROC of the impulse response must include the  $j\omega$  axis. Thus, the ROC of H(s) has to be Re $\{s\}$  < 1.

We can write,

$$H(s) = \frac{s+1-2+2}{s-1} = \frac{s-1}{s-1} + \frac{2}{s-1}$$

$$\therefore \qquad H(s) = 1 + \frac{2}{s-1}$$

$$h(t) = \delta(t) + 2e^t \{-u(-t)\}$$

Also Y(s) has the ROC: Re $\{s\} > -2$

$\therefore$  X(s) must have the ROC:  $-2 < \text{Re}\{s\} < 1$

(i.e, the intersection of the ROCs of Y(s) and H(s)).

$$x(t) = -\frac{2}{3}e^{t}u(-t) + \frac{1}{3}e^{-2t}u(t)$$

# Q.2 (a) Solution:

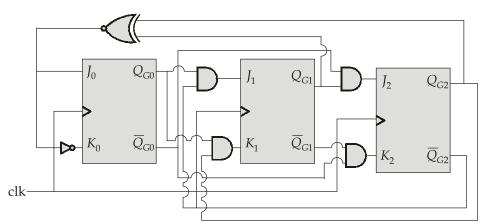

The 3-bit Gray code truth table.

| Bir   | nary Co | ode   | G        | <b>Gray Code</b> |          |  |  |  |  |  |

|-------|---------|-------|----------|------------------|----------|--|--|--|--|--|

| $Q_2$ | $Q_1$   | $Q_0$ | $Q_{G2}$ | $Q_{G1}$         | $Q_{G0}$ |  |  |  |  |  |

| 0     | 0       | 0     | 0        | 0                | 0        |  |  |  |  |  |

| 0     | 0       | 1     | 0        | 0                | 1        |  |  |  |  |  |

| 0     | 1       | 0     | 0        | 1                | 1        |  |  |  |  |  |

| 0     | 1       | 1     | 0        | 1                | 0        |  |  |  |  |  |

| 1     | 0       | 0     | 1        | 1                | 0        |  |  |  |  |  |

| 1     | 0       | 1     | 1        | 1                | 1        |  |  |  |  |  |

| 1     | 1       | 0     | 1        | 0                | 1        |  |  |  |  |  |

| 1     | 1       | 1     | 1        | 0                | 0        |  |  |  |  |  |

20 |

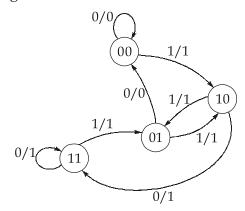

The state diagram for 3-bit Gray code:

The next state table for the 3-bit Gray code:

| Pre      | sent s   | tate     | N          | Next state         |            |  |  |  |  |

|----------|----------|----------|------------|--------------------|------------|--|--|--|--|

| $Q_{G2}$ | $Q_{G1}$ | $Q_{G0}$ | $Q_{G2}^+$ | $Q_{G1}^{\dagger}$ | $Q_{G0}^+$ |  |  |  |  |

| 0        | 0        | 0        | 0          | 0                  | 1          |  |  |  |  |

| 0        | 0        | 1        | 0          | 1                  | 1          |  |  |  |  |

| 0        | 1        | 1        | 0          | 1                  | 0          |  |  |  |  |

| 0        | 1        | 0        | 1          | 1                  | 0          |  |  |  |  |

| 1        | 1        | 0        | 1          | 1                  | 1          |  |  |  |  |

| 1        | 1        | 1        | 1          | 0                  | 1          |  |  |  |  |

| 1        | 0        | 1        | 1          | 0                  | 0          |  |  |  |  |

| 1        | 0        | 0        | 0          | 0                  | 0          |  |  |  |  |

Transition table for JK flip-flop:

|       | p-flop<br>iputs | Transition outputs |   |  |  |  |  |

|-------|-----------------|--------------------|---|--|--|--|--|

| $Q_N$ | $Q_{N+1}$       | J                  | K |  |  |  |  |

| 0     | 0               | 0                  | X |  |  |  |  |

| 0     | 1               | 1                  | X |  |  |  |  |

| 1     | 0               | X                  | 1 |  |  |  |  |

| 1     | 1               | Χ                  | 0 |  |  |  |  |

#### Present state inputs

| $J_2$ | $K_2$ | $J_1$ | $K_1$ | $J_0$ | $K_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | X     | 0     | X     | 1     | X     |

| 0     | X     | 1     | X     | X     | 0     |

| 0     | X     | X     | 0     | X     | 1     |

| 1     | X     | X     | 0     | 0     | X     |

| Χ     | 0     | X     | 0     | 1     | X     |

| Χ     | 0     | X     | 1     | X     | 0     |

| Χ     | 0     | 0     | X     | X     | 1     |

| X     | 1     | 0     | X     | 0     | X     |

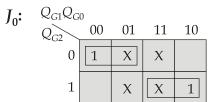

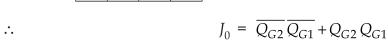

Implementing logic functions for present state J and K inputs:

$$\therefore \qquad \qquad J_2 = Q_{G1} \, \overline{Q_{G0}}$$

$$K_2$$

:  $Q_{G1}Q_{G0}$

$Q_{G2}$

$00$

$01$

$11$

$10$

$0$

$X$

$X$

$X$

$X$

$X$

$$\therefore K_2 = \overline{Q_{G1}} \overline{Q_{G0}}$$

$$\therefore \qquad \qquad J_1 = \overline{Q_{G2}} \, Q_{G0}$$

$$\therefore K_1 = Q_{G2} Q_{G0}$$

$$K_0 = \overline{Q_{G1}} Q_{G2} + \overline{Q_{G2}} Q_{G1}$$

$$= Q_{G2} \oplus Q_{G1}$$

# Q.2 (b) Solution:

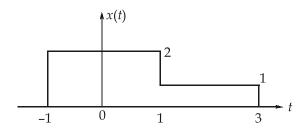

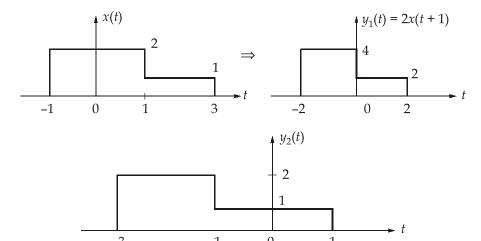

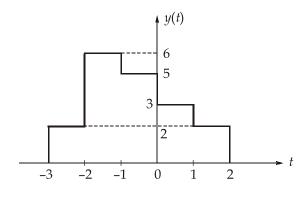

(i) Given,

$$x(t) = \begin{cases} 2, & -1 \le t \le 1 \\ 1, & 1 < t \le 3 \\ 0, & \text{elsewhere} \end{cases}$$

and  $h(t) = 2\delta(t+1) + \delta(t+2)$

Let y(t) be the output of x(t) \* h(t)

$$y(t) = x(t) * [2\delta(t+1) + \delta(t+2)]$$

= 2(x(t) \* \delta(t+1)) + (x(t) \* \delta(t+2))

We know that,

$$x(t) * \delta(t - t_0) = x(t - t_0)$$

Thus,

$$y(t) = 2x(t + 1) + x(t + 2)$$

Let

$$y_1(t) = 2x(t + 1)$$

$$y_2(t) = x(t + 2)$$

$$y(t) = \begin{cases} 2; & -3 \le t \le -2 \\ 6; & -2 \le t \le -1 \\ 5; & -1 \le t \le 0 \\ 3; & 0 \le t < 1 \\ 2; & 1 \le t \le 2 \end{cases}$$

(ii) Given,

$$\frac{dy(t)}{dt} + 10y(t) = \int_{-\infty}^{\infty} x(\tau)z(t-\tau)d\tau - x(t)$$

$$z(t) = e^{-t}u(t) + \delta(t)$$

where

By taking Fourier transform,

$$j\omega Y(\omega) + 10Y(\omega) = X(\omega)Z(\omega) - X(\omega)$$

$$Y(\omega)[10 + j\omega] = X(\omega)[Z(\omega) - 1]$$

$$H(\omega) = \frac{Y(\omega)}{X(\omega)} = \frac{Z(\omega) - 1}{10 + j\omega}$$

Taking Fourier Transform of z(t),

$$Z(\omega) = \frac{1}{1+j\omega} + 1$$

$$Z(\omega) = \frac{2+j\omega}{1+j\omega}$$

$$H(\omega) = \frac{\frac{2+j\omega}{1+j\omega} - 1}{10+j\omega} = \frac{(2+j\omega-1-j\omega)}{(1+j\omega)(10+j\omega)}$$

$$H(\omega) = \frac{1}{(1+j\omega)(10+j\omega)}$$

..

By using partial fraction expansion,

$$\frac{1}{(1+j\omega)(10+j\omega)} = \frac{A}{1+j\omega} + \frac{B}{10+j\omega}$$

$$A = \frac{1}{10+j\omega} \Big|_{j\omega=-1} = \frac{1}{9}$$

$$B = \frac{1}{1+j\omega} \Big|_{j\omega=-10} = \frac{-1}{9}$$

$$H(\omega) = \frac{\frac{1}{9}}{1+i\omega} + \frac{\frac{-1}{9}}{10+j\omega}$$

.

By taking inverse Fourier transform,

$$h(t) = \frac{1}{9}e^{-t}u(t) - \frac{1}{9}e^{-10t}u(t)$$

#### Q.2 (c) Solution:

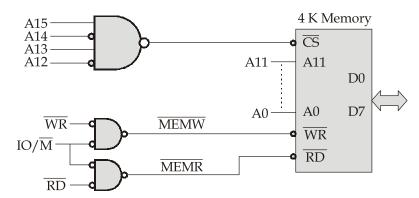

(i) 4 KB memory has  $4 \times 2^{10} = 2^{12}$  address locations and thus, requires 12 address lines for addressing. But 8085 has 16 address lines (A0 - A15). Hence, four of address lines (A15 - A12) are used for address decoding to select the memory block.

Given that starting address for memory is A000H. So, for 4 KB memory, ending address becomes A000H + 0FFFH [4 KB] = AFFFH.

|                | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | <b>A</b> 7 | <b>A6</b> | <b>A</b> 5 | <b>A4</b> | <b>A3</b> | A2 | <b>A1</b> | <b>A</b> 0 |

|----------------|-----|-----|-----|-----|-----|-----|----|----|------------|-----------|------------|-----------|-----------|----|-----------|------------|

| Start Address: | 1   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0          | 0         | 0          | 0         | 0         | 0  | 0         | 0          |

| End Address:   | 1   | 0   | 1   | 0   | 1   | 1   | 1  | 1  | 1          | 1         | 1          | 1         | 1         | 1  | 1         | 1          |

A0-A11 address lines are directly connected to address bus of memory chip. A12-A15 are used for generating chip select for memory chip.

#### Address decoding circuit using $3 \times 8$ decoder.

Address decoding circuit using 3 × 8 decoder

A15 line is used for enabling  $3 \times 8$  decoder chip. A12, A13, A14 lines are connected to  $3 \times 8$  chip as inputs. When these lines are 010, output should be '0'. This is provided at O2 pin of  $3 \times 8$  decoder which is connected to chip select input of memory.

#### Address decoding circuit using only NAND gates:

Address decoding circuit using NAND gates

A15, A14, A13, A12 inputs should be 1010, for enabling the chip. So, the address decoding circuit using NAND Gates is as shown above.

#### (ii) Algorithm:

- 1. Start the program by loading HL register pair with address of memory location.

- 2. Move the first 8-bit number to register B.

- Increment the memory location and move the second 8-bit number to registerC. It acts as the counter for how many times B will be added.

- 4. Add the current content of Register B to the content of the Accumulator (A). The sum is stored back in A.

- 5. Check for carry. If a carry is generated, increment the content of Register D. This accounts for the overflow into the higher byte.

- Decrement the content of Register C and keep on adding the content of register B to the accumulator till C is zero.

- 7. Store the content of the Accumulator (A) which corresponds to the LSB of the final 16-bit result in memory.

- 8. Store the content of register D which corresponds to the MSB of the final 16-bit result in memory.

- 9. Terminate the program.

# Program:

| MVI | D,00H    | Initialize register D to 00H.          |

|-----|----------|----------------------------------------|

| MVI | A, 00H   | Initialize Accumulator content to 00H. |

| LXI | H, 4150H |                                        |

| MOV | В, М     | Get the first number in B-register     |

| INX | Н        | -                                      |

| MOV | C, M     | Get the second number in C-register    |

| LOOP: | ADD | В      | Add content of register A to register B. |

|-------|-----|--------|------------------------------------------|

|       | JNC | NEXT   | JUMP on no carry to NEXT.                |

|       | INR | D      | Increment content of register D.         |

| NEXT: | DCR | C      | Decrement content of register C.         |

|       | JNZ | LOOP   | Jump to LOOP if C is not zero.           |

|       | STA | 4152 H | Store the LSB of result in Memory.       |

|       | MOV | A, D   |                                          |

|       | STA | 4153 H | Store the MSB of result in Memory.       |

|       | HLT |        | Terminate the program.                   |

# Q.3 (a) Solution:

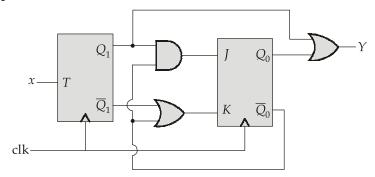

(i) Given sequential circuit,

We can write the following equations for the inputs.

$$T = x \text{ (input)}$$

$$J = Q_1 \overline{Q_0}$$

$$K = \overline{Q_1} + \overline{Q_0}$$

The next states for the above state equations,

| $Q_1$ | $Q_0$ | T = x | $Q_1(t+1)$ | J | K | $Q_0(t+1)$ | Y |

|-------|-------|-------|------------|---|---|------------|---|

| 0     | 0     | 0     | 0          | 0 | 1 | 0          | 0 |

| 0     | 0     | 1     | 1          | 0 | 1 | 0          | 1 |

| 0     | 1     | 0     | 0          | 0 | 1 | 0          | 0 |

| 0     | 1     | 1     | 1          | 0 | 1 | 0          | 1 |

| 1     | 0     | 0     | 1          | 1 | 1 | 1          | 1 |

| 1     | 0     | 1     | 0          | 1 | 1 | 1          | 1 |

| 1     | 1     | 0     | 1          | 0 | 0 | 1          | 1 |

| 1     | 1     | 1     | 0          | 0 | 0 | 1          | 1 |

The state table is,

|       |       | Nex   | t state | Outpu | ıt (Y) |

|-------|-------|-------|---------|-------|--------|

| $Q_1$ | $Q_0$ | x = 0 | x = 1   | x = 0 | x = 1  |

| 0     | 0     | 00    | 10      | 0     | 1      |

| 0     | 1     | 00    | 10      | 0     | 1      |

| 1     | 0     | 11    | 01      | 1     | 1      |

| 1     | 1     | 11    | 01      | 1     | 1      |

The required state diagram is,

$$x[n] = a^n \sin(\omega_0 n) u[n]$$

Let

$$g[n] = a^n u[n]$$

Take z-transform on both sides,

$$G(z) = \frac{1}{1 - az^{-1}}; ROC : |z| > |a|$$

$$\therefore x[n] = g[n] \cdot \sin(\omega_0 n)$$

$$= g[n] \left[ \frac{e^{j\omega_0 n} - e^{-j\omega_0 n}}{2j} \right] = \frac{1}{2j} g[n] e^{j\omega_0 n} - \frac{1}{2j} g[n] e^{-j\omega_0 n}$$

Take *z*-transform on both sides,

$$X(z) = \frac{1}{2j} \left[ G\left(\frac{z}{e^{j\omega_0}}\right) - G\left(\frac{z}{e^{-j\omega_0}}\right) \right]; |z| > \left| e^{\pm j\omega_0} \right| \cdot |a|$$

$\therefore$  Scaling in z-domain property:  $\alpha^n x[n] \leftrightarrow X(\frac{z}{\alpha})$ ; ROC:  $|\alpha|R$

Where 'R' is the ROC of x[n]

$$\Rightarrow X(z) = \frac{1}{2j} \left[ \frac{1}{1 - a \left( \frac{z}{e^{j\omega_0}} \right)^{-1}} - \frac{1}{1 - a \left( \frac{z}{e^{-j\omega_0}} \right)^{-1}} \right]; |z| > |a|$$

$$X(z) = \frac{1}{2j} \left[ \frac{1}{1 - a e^{j\omega_0} z^{-1}} - \frac{1}{1 - a e^{-j\omega_0} z^{-1}} \right]$$

$$X(z) = \frac{1}{2j} \left[ \frac{1 - a e^{-j\omega_0} z^{-1} - 1 + a e^{j\omega_0} z^{-1}}{1 - a e^{-j\omega_0} z^{-1} - a e^{j\omega_0} z^{-1} + a^2 z^{-2}} \right]$$

$$X(z) = \frac{1}{2j} \left[ \frac{az^{-1} \left( e^{j\omega_0} - e^{-j\omega_0} \right)}{1 - a z^{-1} \left( e^{-j\omega_0} + e^{j\omega_0} \right) + a^2 z^{-2}} \right]$$

$$X(z) = \left[ \frac{az^{-1} \sin \omega_0}{1 - 2a z^{-1} \cos \omega_0 + a^2 z^{-2}} \right]; |z| > |a|$$

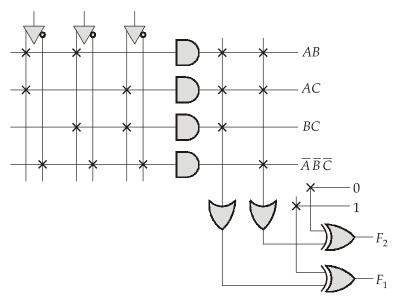

#### Q.3 (b) Solution:

(i) Given,

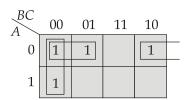

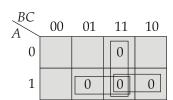

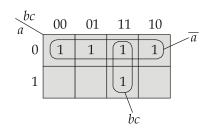

K-map for  $F_1$ :

$$F_1 = \overline{B}\overline{C} + \overline{A}\overline{B} + \overline{A}\overline{C}$$

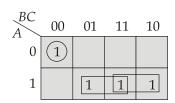

K-map for  $F_2$ :

$$F_2 = AB + AC + \overline{A}\overline{B}\overline{C}$$

K-map for  $\overline{F_1}$ :

$$\overline{F_1} = AB + AC + BC$$

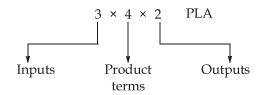

# PLA implementation:

# PLA programming table:

|   | Product                                | Inputs |   |   | Outputs |       |

|---|----------------------------------------|--------|---|---|---------|-------|

|   | term                                   | A      | В | С | $F_1$   | $F_2$ |

| 1 | AB                                     | 1      | 1 | _ | 1       | 1     |

| 2 | AC                                     | 1      | - | 1 | 1       | 1     |

| 3 | ВС                                     | _      | 1 | 1 | 1       | _     |

| 4 | $\overline{A}\overline{B}\overline{C}$ | 0      | 0 | 0 | _       | 1     |

# (ii) Given,

reference voltage,

$$V_R = 12 \text{ V}$$

fixed count =  $010110_2 = (22)_{10}$   $N = 6 \text{ bit}$

Discharge time of dual slope ADC,

$$T_2 = \frac{V_{in} \times T_1}{V_R}$$

$$V_{in, \text{max}} = \frac{V_R \times T_2}{T_1}$$

$$T_2 = 2^N \times T = 2^6 \times T$$

$$V_{in, \text{max}} = \frac{(12) \times 2^6 \times T}{22T} = 34.9 \text{ V}$$

# MADE EASY

#### Q.3 (c) Solution:

(i)

$Q_0$  toggles only when clock changes from '1' to '0'. i.e.,  $Q_0$  toggles for every clock pulse.

$Q_1$  toggles only when  $Q_0$  changes from '1' to '0'.

$Q_2$  toggles only when  $Q_1$  changes from '0' to '1'.

$Q_3$  toggles only when  $Q_2$  changes from '0' to '1'.

|                                         | $Q_3$ | $Q_2$ | $Q_1$ | $Q_0$ | Decimal equivalent |

|-----------------------------------------|-------|-------|-------|-------|--------------------|

| Initially                               | 0     | 0     | 0     | 0     | 0                  |

| $1^{\rm st}$ clk $\rightarrow$          | 0     | 0     | 0     | 1     | 1                  |

| $2^{nd}$ clk $\rightarrow$              | 1     | 1     | 1     | 0     | 14                 |

| $3^{\rm rd}$ clk $\rightarrow$          | 1     | 1     | 1     | 1     | 15                 |

| $4^{th} clk \rightarrow$                | 1     | 1     | 0     | 0     | 12                 |

| $5^{\text{th}} \text{clk} \rightarrow$  | 1     | 1     | 0     | 1     | 13                 |

| $6^{th} clk \rightarrow$                | 1     | 0     | 1     | 0     | 10                 |

| $7^{\text{th}} \text{clk} \rightarrow$  | 1     | 0     | 1     | 1     | 11                 |

| $8^{th}$ clk $\rightarrow$              | 1     | 0     | 0     | 0     | 8                  |

| $9^{th}$ clk $\rightarrow$              | 1     | 0     | 0     | 1     | 9                  |

| $10^{\text{th}} \text{clk} \rightarrow$ | 0     | 1     | 1     | 0     | 6                  |

| $11^{\text{th}} \text{clk} \rightarrow$ | 0     | 1     | 1     | 1     | 7                  |

| $12^{\text{th}} \text{clk} \rightarrow$ | 0     | 1     | 0     | 0     | 4                  |

| $13^{\text{th}} \text{clk} \rightarrow$ | 0     | 1     | 0     | 1     | 5                  |

| $14^{\text{th}} \text{clk} \rightarrow$ | 0     | 0     | 1     | 0     | 2                  |

| $15^{\text{th}} \text{clk} \rightarrow$ | 0     | 0     | 1     | 1     | 3                  |

| $16^{\text{th}} \text{clk} \rightarrow$ | 0     | 0     | 0     | 0     | 0                  |

(ii) Frequency of

$$Q_0 = \frac{f_{\rm clk}}{2} = \frac{160 \, \rm kHz}{2} = 80 \, \rm kHz$$

Frequency of  $Q_2 = \frac{f_{\rm clk}}{8} = \frac{160 \, \rm kHz}{8} = 20 \, \rm kHz$

(iii)

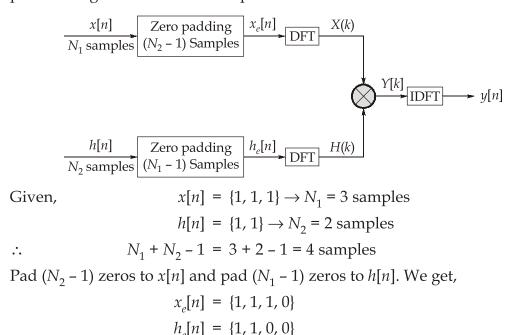

#### Q.4 (a) Solution:

(i) The circular convolution of two sequences of lengths  $N_1$  and  $N_2$  respectively, can be made equal to the linear convolution of the two sequences by zero padding both the sequences, so that they both consist of  $(N_1 + N_2 - 1)$  samples as shown below.

Then find the DFT of both the sequences having  $(N_1 + N_2 - 1)$  samples individually. Multiply the DFTs of both the sequences and find the inverse DFT of the obtained product to get the convolved sequence.

DFT of  $x_e[n]$  and  $h_e[n]$  is calculated as below,

$$X(k) = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & -j & -1 & j \\ 1 & -1 & 1 & -1 \\ 1 & j & -1 & -j \end{bmatrix} \begin{bmatrix} 1 \\ 1 \\ 1 \\ 0 \end{bmatrix} = \begin{bmatrix} 1+1+1+0 \\ 1-j-1+0 \\ 1-1+1+0 \\ 1+j-1+0 \end{bmatrix} = \begin{bmatrix} 3 \\ -j \\ 1 \\ j \end{bmatrix}$$

$$H(k) = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & -j & -1 & j \\ 1 & -1 & 1 & -1 \\ 1 & j & -1 & -j \end{bmatrix} \begin{bmatrix} 1 \\ 1 \\ 0 \\ 0 \end{bmatrix} = \begin{bmatrix} 1+1+0+0 \\ 1-j+0+0 \\ 1-1+0+0 \\ 1+j+0+0 \end{bmatrix} = \begin{bmatrix} 2 \\ 1-j \\ 0 \\ 1+j \end{bmatrix}$$

Take sample by sample product to get Y(k):

$$Y(k) = X(k) \cdot H(k)$$

$$k = 0 : Y(0) = X(0) \cdot H(0) = (3) \cdot (2) = 6$$

$$k = 1 : Y(1) = X(1) \cdot H(1) = (-j) \cdot (1 - j) = (-1 - j)$$

$$k = 2 : Y(2) = X(2) \cdot H(2) = (1) \cdot (0) = 0$$

$$k = 3 : Y(3) = X(3) \cdot H(3) = (j) \cdot (1 + j) = (-1 + j)$$

$$\therefore y[n] = \frac{1}{N} [W^{-1}] \times [Y(k)] = \frac{1}{4} \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & j & -1 & -j \\ 1 & -1 & 1 & -1 \\ 1 & -j & -1 & j \end{bmatrix} \begin{bmatrix} 6 \\ -1 - j \\ 0 \\ -1 + j \end{bmatrix}$$

$$= \frac{1}{4} \begin{bmatrix} 6-1-j+0-1+j \\ 6-j+1+0+j+1 \\ 6+1+j+0+1-j \\ 6+j-1+0-j-1 \end{bmatrix} = \frac{1}{4} \begin{bmatrix} 4 \\ 8 \\ 8 \\ 4 \end{bmatrix}$$

$$\Rightarrow \qquad y[n] = \{1, 2, 2, 1\}$$

(ii) We know, the Discrete Fourier Series (DFS) coefficients of signal x[n] is given by,

$$C_k = \frac{1}{N} \sum_{n=0}^{N-1} x[n] e^{-j\omega_0 kn}$$

Where, 'N' is the fundamental period and ' $\omega_0$ ' is the fundamental frequency,

$$\omega_0 = \frac{2\pi}{N}$$

$$C_k = \frac{1}{N} \sum_{n=0}^{N-1} x[n] e^{-j\frac{2\pi}{N}kn} \qquad ...(i)$$

$\Rightarrow$

We know, the Discrete Fourier Transform (DFT) of signal x[n] is,

$$X(k) = \sum_{n=0}^{N-1} x[n] e^{-j\frac{2\pi}{N}kn} \qquad ...(ii)$$

On comparing equations (i) and (ii), the relationship between  $C_k$  and X(k) is,

$$C_k = \frac{X(k)}{N}$$

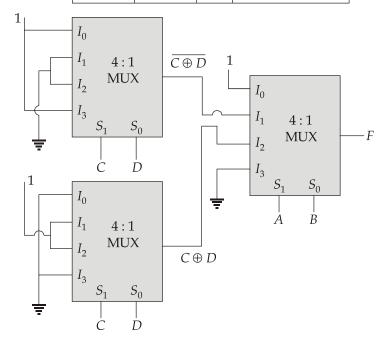

# Q.4 (b) Solution:

(i)

$$F(A, B, C, D) = \Sigma m(0, 1, 2, 3, 4, 7, 9, 10)$$

Consider a 4 : 1 MUX with select lines as AB.

| A | В | С | D | F | Input to 4:1 MUX              |

|---|---|---|---|---|-------------------------------|

| 0 | 0 | 0 | 0 | 1 |                               |

| 0 | 0 | 0 | 1 | 1 | $I_0 = 1$                     |

| 0 | 0 | 1 | 0 | 1 | 10 1                          |

| 0 | 0 | 1 | 1 | 1 |                               |

| 0 | 1 | 0 | 0 | 1 |                               |

| 0 | 1 | 0 | 1 | 0 | $I_1 = \overline{C \oplus D}$ |

| 0 | 1 | 1 | 0 | 0 | $I_1 - C \oplus D$            |

| 0 | 1 | 1 | 1 | 1 |                               |

| 1 | 0 | 0 | 0 | 0 |                               |

| 1 | 0 | 0 | 1 | 1 | $I_2 = C \oplus D$            |

| 1 | 0 | 1 | 0 | 1 | $I_2 - C \oplus D$            |

| 1 | 0 | 1 | 1 | 0 |                               |

| 1 | 1 | 0 | 0 | 0 |                               |

| 1 | 1 | 0 | 1 | 0 |                               |

| 1 | 1 | 1 | 0 | 0 | $I_3 = 0$                     |

| 1 | 1 | 1 | 1 | 0 |                               |

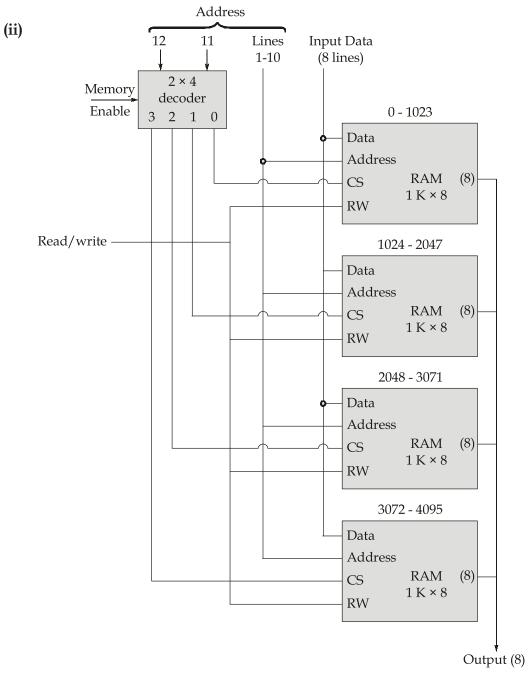

The 4 K word memory requires 12-bit address. The 10 least significant bits of the address are applied to the address input of all four chips. The other two most significant bits are applied to a  $2 \times 4$  decoder. The four outputs of the decoder are applied to the CS inputs of each chip. The memory is disabled when the memory enable input of the decoder is equal to 0. This causes all four outputs of the decoder to be in the 0 state and none of the chips are selected. When the decoder is enabled address bits 12 and 11 determine the particular chip that is selected.

If bits 12 and 11 are equal to 00, the first RAM chip is selected. The remaining 10 address bits select a word within the chip in the range from 0 to 1023. The next 1024 words are selected from the second RAM chip with a 12-bit address that starts with 01 and followed by the ten bits from the common address lines.

#### Q.4 (c) Solution:

(i) Algorithm: The algorithm for converting a BCD number into its binary equivalent first unpacks the BCD number into two digits tens digit (upper nibble) and units digit (lower nibble). The tens digit is multiplied by 10D or 0AH in hexadecimal form, and then the unit digit is added with the result. The result is stored in 9001 H.

#### Program

MOV DPTR, # 9000H; Point the data pointer to the location of the BCD number.

MOVX A, @ DPTR ; Move the BCD number to the accumulator.

MOV R0, A ; Copy BCD number to R0 register.

ANL A, # 0FH ; Mask the higher-order four bits.

MOV R1, A ; Save the (lower nibble) in register R1.

MOV A, R0 ; Bring the data again to register A.

ANL A, # F0H ; Mask the lower-order four bits.

SWAP A ; Bring the higher four bits (upper nibble) to the lower

four bits.

MOV B, # 0AH ; Store 10D in register B.

MUL AB ; Multiply the tens digit of BCD number by 10.

ADD A, R1; Add the result with the lower nibble (unit digit).

INC DPTR ; Increment the data pointer to the next location 9001H.

MOVX @ DPTR, A ; Save the result at the location 9001H pointed by the data

pointer.

WAIT: SJMP WAIT ; Terminate program execution.

(ii) Given,

$$\sum_{i=1}^{10} i = 1 + 2 + 3 + \dots + 9 + 10$$

# Algorithm:

- 1. Initialize a counter (CX) to 10 = 000AH.

- 2. Initialize a sum register (AX) to 0.

- 3. Loop while CX is less than or equal to 10:

- Add the current value of the counter (CX) to the sum (AX)

- Decrement the counter (CX).

- 4. The final sum will be in AX.

#### **Program:**

START:

MOV CX,0001H ; CX = 1

MOV AX,0000H ; AX = 0

CONTINUE: ADD AX, CX;  $AX \leftarrow AX + CX$

INC CX ;  $CX \leftarrow CX + 1$

CMP CX, 000AH ; Compare CX content with 10

JBE CONTINUE; Jump if contents of CX is below or equal

to '10'.

HLT

END:

# Section B : Digital Circuits + Signals and Systems + Microprocessors & Microcontroller

# Q.5 (a) Solution:

(i) Given,

$$f(t) = 2e^{-t}\cos 10t - t^4 + 6e^{-(t-10)}; t > 0$$

Let,  $f_1(t) = 2e^{-t}\cos 10t \ u(t)$

$f_2(t) = -t^4 u(t)$

$f_2(t) = 6e^{-(t-10)}u(t)$

Thus,  $f(t) = f_1(t) + f_2(t) + f_3(t)$

Taking Laplace transform,

$$F(s) = F_1(s) + F_2(s) + F_3(s)$$

For  $f_1(t)$ ;

We know that,  $\cos \omega_0 t \ u(t) \xleftarrow{L} \frac{s}{s^2 + \omega_0^2}$ ; Re $\{s\} > 0$

$$e^{s_0t}x(t) \longleftrightarrow X(s-s_0)$$

$\therefore \qquad \cos 10t \, u(t) \stackrel{L}{\longleftrightarrow} \frac{s}{s^2 + 100}$

$$e^{-t}\cos 10tu(t) \longleftrightarrow \frac{s+1}{(s+1)^2+100}$$

; Re{s} > -1

$$2e^{-t}\cos 10tu(t) \stackrel{L}{\longleftrightarrow} \frac{2(s+1)}{(s+1)^2+100}$$

; ROC<sub>1</sub>: Re{s} > -1

For  $f_2(t)$ ;

We know that,

$$t^k u(t) \longleftrightarrow \frac{k!}{s^{k+1}}$$

; Re{s} > 0

$$-t^4u(t) \stackrel{L}{\longleftrightarrow} \frac{-4!}{s^5}$$

; Re $\{s\} > 0$

$$-t^4u(t) \stackrel{L}{\longleftrightarrow} \frac{-24}{s^5}$$

; ROC<sub>2</sub>: Re{s} > 0

For  $f_3(t)$ :

$$f_3(t) = 6e^{-(t-10)}u(t)$$

$$= 6e^{-t} \cdot e^{10} \cdot u(t)$$

$$= 6e^{10} e^{-t}u(t)$$

$$\therefore \qquad 6e^{10} \cdot e^{-t}u(t) \stackrel{L}{\longleftrightarrow} 6e^{10} \frac{1}{s+1}; ROC_3 : Re\{s\} > -1$$

From (i), (ii) and (iii),

$$F(s) = \frac{2(s+1)}{(s+1)^2 + 100} - \frac{24}{s^5} + \frac{6e^{10}}{s+1}; ROC: ROC_1 \cap ROC_2 \cap ROC_3: Re\{s\} > 0$$

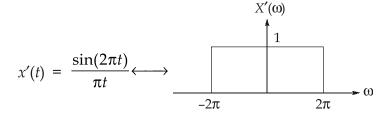

$$x(t) = \frac{\sin(2\pi t)}{\pi(t-1)}$$

We know that,  $Arect\left(\frac{t}{T}\right)\longleftrightarrow AT\frac{\sin(\omega T/2)}{\omega T/2}$

Using the principle of duality,

$$AT \frac{\sin(tT/2)}{tT/2} \longleftrightarrow 2\pi A rect \left(-\frac{t}{T}\right) = 2\pi A rect \left(\frac{t}{T}\right)$$

Thus,

$$x'(t) = \frac{\sin(2\pi t)}{\pi t} \longleftrightarrow u(\omega + 2\pi) - u(\omega - 2\pi)$$

We have,

$$x(t) = \frac{\sin(2\pi t)}{\pi (t-1)} = \frac{\sin(2\pi t - 2\pi)}{\pi (t-1)} = \frac{\sin(2\pi (t-1))}{\pi (t-1)} = x'(t-1)$$

We know that,

$$x(t) \longleftrightarrow x(t) \longleftrightarrow x(t-1) \longleftrightarrow x($$

$X(\omega) = e^{-j\omega}[u(\omega + 2\pi) - u(\omega - 2\pi)]$

# Q.5 (b) Solution:

For the given 4-bit R-2R ladder converter output voltage,

$$V_{0} = V_{R} \cdot \frac{R_{f}}{R} \left[ \frac{b_{1}}{2^{1}} + \frac{b_{2}}{2^{2}} + \frac{b_{3}}{2^{3}} + \frac{b_{4}}{2^{4}} \right]$$

Given that,

$$V_{R} = 10 \text{ V}$$

$$R = 5 \text{ k}\Omega$$

value of 1 LSB = 1 volt

$$1 = 10 \times \frac{R_{f}}{5 \times 10^{3}} \cdot \left[ \frac{1}{2^{4}} \right]$$

$$R_{f} = \frac{5 \times 10^{3} \times 2^{4}}{10}$$

$$= 500 \times 2^{4} = 8000 \Omega$$

$$R_{f} = 8 \text{ k}\Omega$$

(ii) For binary value of 1000

$$b_1 = 1; b_2 = b_3 = b_4 = 0$$

$$8 = 10 \times \frac{R_f}{5 \times 10^3} \left[ \frac{1}{2} \right]$$

$$R_f = \frac{8 \times 2 \times 5 \times 10^3}{10} = 8 \text{ k}\Omega$$

(iii) Thus for getting a full scale voltage of 10 V,

$$b_1 = b_2 = b_3 = b_4 = 1$$

$$\frac{R_f \times 10}{5 \times 10^3} \left[ \frac{1}{2} + \frac{1}{2^2} + \frac{1}{2^3} + \frac{1}{2^4} \right] = 10$$

$$\frac{R_f}{5 \times 10^3} [0.9375] = 1$$

$$R_f = \frac{5 \times 10^3}{0.9375} = 5.333 \text{ k}\Omega$$

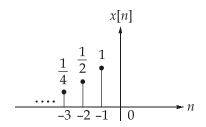

# Q.5 (c) Solution:

We know,

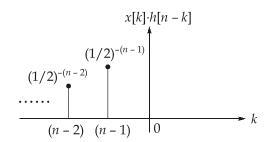

$$y[n] = x[n] * h[n] = \sum_{k=-\infty}^{+\infty} x[k] \cdot h[n-k]$$

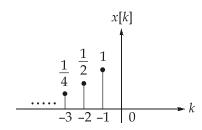

Given,

$$x[n] = \left(\frac{1}{2}\right)^{(-n-1)} u[-n-1] = \left(\frac{1}{2}\right)^{-1} \left(\frac{1}{2}\right)^{-n} u[-n-1] = 2\left(\frac{1}{2}\right)^{-n} u[-n-1]$$

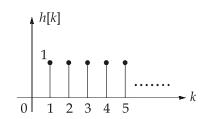

and  $h[n] = u[n-1]$

Limits of x[n]:  $-\infty \le n \le -1$

Limits of  $h[n]: 1 \le n \le \infty$

The range of the convoluted signal of two discrete-time signals is the sum of the range of the individual signals. Thus,

Limits of

$$y[n]$$

:  $(-\infty + 1) \le n \le (-1 + \infty) = -\infty \le n \le \infty$

# Plot x[n] and h[n]:

# Change the n-axis to k-axis:

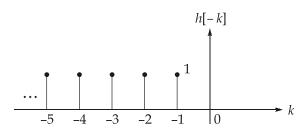

Find time reversal plot of h[k]:

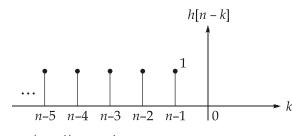

Plot h[n - k]:

Case (i):

$$\Rightarrow$$

$$(n-1) < -1$$

$$n < 0$$

$$y[n] = \sum_{k=-\infty}^{+\infty} x[k] \cdot h[n-k]$$

$\rightarrow$

$$y[n] = \sum_{k=-\infty}^{n-1} 2\left(\frac{1}{2}\right)^{-k} \cdot (1)$$

$$y[n] = 2 \sum_{k=-\infty}^{n-1} \left(\frac{1}{2}\right)^{-k}$$

Put (n - 1) - k = p

Limits:

$$k = n - 1 \Rightarrow p = 0$$

$$k = -\infty \Longrightarrow p = \infty$$

..

$$y[n] = 2\sum_{p=\infty}^{0} \left(\frac{1}{2}\right)^{p-(n-1)} = 2\left(\frac{1}{2}\right)^{-(n-1)} \sum_{p=\infty}^{0} \left(\frac{1}{2}\right)^{p}$$

$$= 2(2)^{(n-1)} \sum_{p=0}^{\infty} \left(\frac{1}{2}\right)^p = 2^n \sum_{p=0}^{\infty} \left(\frac{1}{2}\right)^p$$

$$= 2^{n} \left[ \frac{1}{1 - \frac{1}{2}} \right] = 2^{n} [2] = 2^{n+1}$$

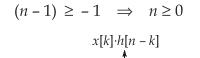

Case (ii): (n-1)

$$y[n] = \sum_{k=-\infty}^{+\infty} x[k] \cdot h[n-k]$$

$$y[n] = \sum_{k=-\infty}^{-1} 2\left(\frac{1}{2}\right)^{-k} \cdot (1)$$

Put -k = p

$\Rightarrow$

$$y[n] = \sum_{p=\infty}^{1} 2\left(\frac{1}{2}\right)^{p} = 2\sum_{p=1}^{\infty} \left(\frac{1}{2}\right)^{p} = 2\left[\sum_{p=0}^{\infty} \left(\frac{1}{2}\right)^{p} - 1\right]$$

$$= 2\left[\frac{1}{1 - \frac{1}{2}}\right] - 2 = 4 - 2 = 2$$

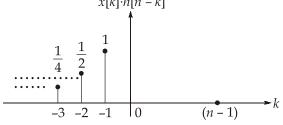

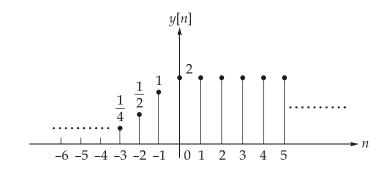

$y[n] = 2^{n+1} \quad ; \quad n < 0$  $= 2 \quad ; \quad n \ge 0$

#### Q.5 (d) Solution:

- **1.**  $\overline{\text{BHE}/\text{S7}}$ : The bus high enable  $(\overline{\text{BHE}})$  pin is used in the 8086 to enable the most significant data bus  $(D_{15} D_8)$  during a read/write operation. It goes low for the data transfer over  $D_{15}$ - $D_8$  and is used to derive chip selects of odd address memory bank or peripherals.

- 2. MN/MX: The MN/MX pin is used to select either the minimum mode (single processor) or the maximum mode (multiprocessor) operation for the 8086. This is achieved by connecting this pin to either +5V directly (for minimum mode) or to the ground (for maximum mode).

- **TEST**: The Test pin is an input that is tested by the WAIT instruction. If the Test pin is at logic 0, the WAIT instruction functions as a NOP (no operation) instruction. If the Test pin is at logic 1, the WAIT instruction waits for the Test pin to become logic 0. This pin is often connected to the BUSY pin of the 8087 (numeric coprocessor) to perform floating-point operations.

- **4. READY**: This input is used to insert wait states into the timing cycle of the 8086 such that it is extended by a number of clock periods. If the READY pin is at logic 1, it has no effect on the operation of the microprocessor. If it is at logic 0, the 8086 enters the wait state and remains idle. This pin is used to interface the slowly operating peripherals with the 8086.

- **5. RESET:** This input causes the 8086 to reset, if it is held at logic 1 for a minimum of four clocking periods. Whenever the 8086 is reset, CS and IP are initialized to FFFFH and 0000H, respectively, and all other registers are initialized to 0000H. This causes the 8086 to begin executing instructions from the memory address FFFF0H and IF flag is cleared.

- **6. INTR:** The interrupt request (INTR) is a level-triggered hardware interrupt, which depends on the status of IF. When IF = 1, if INTR is held high (i.e., logic 1), the 8086 gets interrupted. When IF = 0, INTR is disabled.

# Q.5 (e) Solution:

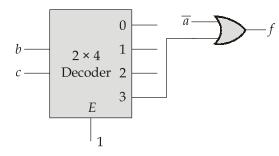

(i) Given, Boolean function,  $f(a, b, c) = \Sigma m(0, 1, 2, 3, 7)$ By using three variable K-map,

$$f = \overline{a} + bc$$

By using 2 × 4 decoder and OR gates.

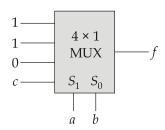

(ii) Given Boolean function,  $f(a, b, c) = \Sigma m(0, 1, 2, 3, 7)$ By using  $4 \times 1$  multiplexer

$$f = \overline{a} \, \overline{b} + \overline{a} \, b + abc$$

$$= \overline{a} (\overline{b} + b) + abc$$

$$f = \overline{a} + bc$$

(iii)

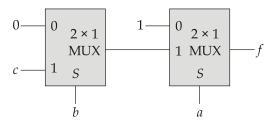

$$f(a, b, c) = \sum m(0, 1, 2, 3, 7)$$

$$f = \overline{a} + bc$$

By using a minimal network of 2 × 1 multiplexers

#### Q.6 (a) Solution:

(i) MOV AL, 29 H ; Move the first BCD data to AL.

ADD AL, 98 H ; Add the second BCD data to first BCD data.

DAA ; Decimal-adjust AL to get the result in BCD form.

MOV BX, 2000 H ; BX  $\leftarrow$  2000 H

MOV DS, BX; Initialize DS with 2000 H (DS holds the base address

for the data segment)

MOV [3000H], AL ; Store the content of AL, which is the lower byte of

the result in the memory.

JC L1 ; If the carry flag is 1, go to L1

MOV [3001 H], 00H; Store 00H in the memory, since the carry is 0.

JMP L2 ; Go to L2

L1: MOV [3001H], 01H; Store 01H in the memory, since the carry is 1.

L2: HLT; Stop

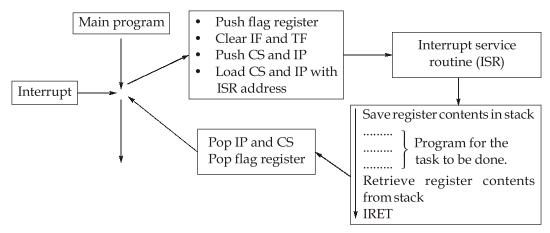

- (ii) After executing each instruction in a program, the 8086 checks if any interrupt has been requested. If an interrupt has been requested, the 8086 processes it by performing the following series of steps:

- 1. Pushes the content of the 16-bit flag register onto the stack to preserve the status of the interrupt (IF) and trap flags (TF), by decrementing the stack pointer (SP) by 2.

- 2. Disables the INTR interrupt by clearing Interrupt Flag (IF) in the flag register.

- 3. Resets TF in the flag register, to disable the single step or trap interrupt.

- 4. Pushes the content of the code segment (CS) register onto the stack by decrementing SP by 2.

- 5. Pushes the content of the instruction pointer (IP) onto the stack by decrementing SP by 2.

- 6. Performs an indirect far jump to the start of the interrupt service routine (ISR) corresponding to the received interrupt. An IRET instruction at the end of the interrupt service routine returns execution to main program.

Processing of an interrupt by the 8086

# Q.6 (b) Solution:

(i) Given,

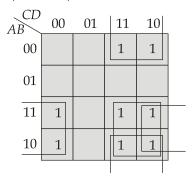

$$f(A, B, C, D) = \Sigma m(2, 3, 8, 10, 11, 12, 14, 15)$$

$$f = AC + A\overline{D} + \overline{B}C$$

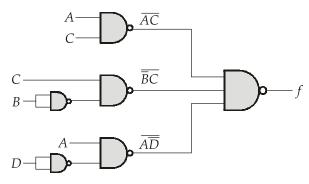

By using NAND gates, realizing above minimized expression,

$$\overline{\overline{f}} = \overline{\overline{AC} + A\overline{D} + \overline{BC}}$$

$$= \overline{\overline{AC} \cdot \overline{A\overline{D}} \cdot \overline{\overline{BC}}}$$

(ii) Truth table for the given logic circuit:

Let output of 2 × 1 MUXs are  $Y_{0'}$ ,  $Y_{1'}$ ,  $Y_{2}$  and  $Y_{3}$  respectively.

$$Y_0 = \overline{S_0}D_0 + S_0D_1$$

$$Y_1 = \overline{S_0}D_2 + S_0D_3$$

$$Y_2 = \overline{S_0}D_4 + S_0D_5$$

$$Y_3 = \overline{S_0}D_6 + S_0D_7$$

.. Output logic function

$$Y = \overline{S_2} \overline{S_1} Y_0 + \overline{S_2} S_1 Y_1 + S_2 \overline{S_1} Y_2 + S_2 S_1 Y_3$$

$$Y = \overline{S_2} \overline{S_1} (\overline{S_0} D_0 + S_0 D_1) + \overline{S_2} S_1 (\overline{S_0} D_2 + S_0 D_3)$$

$$+ S_2 S_1 (\overline{S_0} D_4 + S_0 D_5) + S_2 S_1 (\overline{S_0} D_6 + S_0 D_7)$$

## Q.6 (c) Solution:

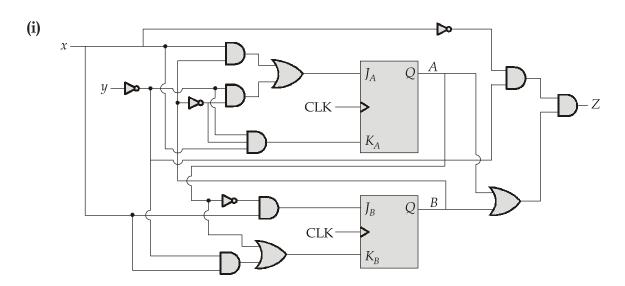

Given,  $J_A = Bx + \overline{B}\overline{y}$ ;  $K_A = \overline{B}x\overline{y}$ ;  $J_B = \overline{A}x$ ;  $K_B = A + x\overline{y}$ ;  $Z = A\overline{x}\overline{y} + B\overline{x}\overline{y}$

| (ii) |   | sent<br>ate | Input |   | Next State |        | O/P | Flip flop input |       | uts   |       |

|------|---|-------------|-------|---|------------|--------|-----|-----------------|-------|-------|-------|

|      | A | В           | x     | у | A(t+1)     | B(t+1) | Z   | $J_A$           | $K_A$ | $J_B$ | $K_B$ |

|      | 0 | 0           | 0     | 0 | 1          | 0      | 0   | 1               | 0     | 0     | 0     |

|      | 0 | 0           | 0     | 1 | 0          | 0      | 0   | 0               | 0     | 0     | 0     |

|      | 0 | 0           | 1     | 0 | 1          | 1      | 0   | 1               | 1     | 1     | 1     |

|      | 0 | 0           | 1     | 1 | 0          | 1      | 0   | 0               | 0     | 1     | 0     |

|      | 0 | 1           | 0     | 0 | 0          | 1      | 0   | 0               | 0     | 0     | 0     |

|      | 0 | 1           | 0     | 1 | 0          | 1      | 0   | 0               | 0     | 0     | 0     |

|      | 0 | 1           | 1     | 0 | 1          | 0      | 0   | 1               | 0     | 1     | 1     |

|      | 0 | 1           | 1     | 1 | 1          | 1      | 1   | 1               | 0     | 1     | 0     |

|      | 1 | 0           | 0     | 0 | 1          | 0      | 0   | 1               | 0     | 0     | 1     |

|      | 1 | 0           | 0     | 1 | 1          | 0      | 0   | 0               | 0     | 0     | 1     |

|      | 1 | 0           | 1     | 0 | 0          | 0      | 0   | 1               | 1     | 0     | 1     |

|      | 1 | 0           | 1     | 1 | 1          | 0      | 1   | 0               | 0     | 0     | 1     |

|      | 1 | 1           | 0     | 0 | 1          | 0      | 0   | 0               | 0     | 0     | 1     |

|      | 1 | 1           | 0     | 1 | 1          | 0      | 0   | 0               | 0     | 0     | 1     |

|      | 1 | 1           | 1     | 0 | 1          | 0      | 0   | 1               | 0     | 0     | 1     |

|      | 1 | 1           | 1     | 1 | 1          | 0      | 1   | 1               | 0     | 0     | 1     |

(iii) For a JK flip flop,

$$Q(t+1) = J\bar{Q}(t) + \bar{K}Q(t)$$

State equations for *A* and *B*,

$$A(t+1) = J_A \overline{A} + \overline{K}_A A$$

$$= \left[ Bx + \overline{B} \overline{y} \right] \overline{A} + \left( \overline{B} x \overline{y} \right) A$$

$$= \overline{A} Bx + \overline{A} \overline{B} \overline{y} + A \left[ B + \overline{x} + y \right]$$

$$= \overline{A} Bx + \overline{A} \overline{B} \overline{y} + AB + A \overline{x} + Ay$$

$$A(t+1) = \overline{A} \overline{B} \overline{y} + Ay + A \overline{x} + AB + Bx$$

$$B(t+1) = J_B \overline{B} + \overline{K}_B B$$

$$= \overline{A} x \overline{B} + \left( \overline{A} + x \overline{y} \right) B$$

$$= \overline{A} x \overline{B} + B \left[ \overline{A} \left( x \overline{y} \right) \right]$$

$$= \overline{A} x \overline{B} + \overline{A} B (\overline{x} + y)$$

$$B(t+1) = \overline{A} \overline{B} x + \overline{A} B \overline{x} + \overline{A} B y$$

## Q.7 (a) Solution:

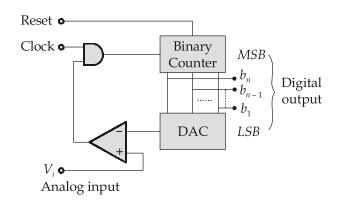

(i) The counter type *ADC* is constructed using only one comparator with a variable reference voltage. The variable reference voltage can be obtained by a sequence or binary counter and a *DAC*. The block diagram for an *n*-bit counter type *ADC* is shown below,

#### The operation of the counter type ADC:

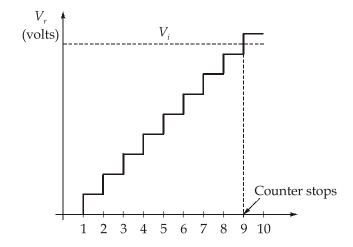

The n-bit binary counter is initially set to 0 by the reset switch which is normally active low. Therefore, the digital output is zero and the analog equivalent  $V_r$  is also 0. When reset signal is released (HIGH), the clock pulses gated through the AND gate are counted by the binary counter. The DAC converts the digital output to an analog voltage and connects it as the inverting input to the comparator. The output of the comparator enables the AND gate to pass the clock. The number of counted pulses increases with time and the analog output  $V_r$  from DAC is a rising staircase waveform.

The counting will continue until the reference voltage  $V_r$  equals and just rises more than  $V_i$ . Then the comparator output becomes low and this disables the AND gate from passing the clock. The counting steps at the instance  $V_i < V_r$  and at that instant the digital output represents the analog input voltage  $V_i$ . Then the clock is inhibited, the counter stops its progress and the conversion is said to be complete. The numbers stored in the n-bit counter is the equivalent n-bit digital data for the given analog input voltage.

#### **Advantages:**

- The counter type *ADC* is very simple and needs less hardware compared to the simultaneous type *ADC*.

- This is suitable for digitizing applications with high resolution.

#### **Disadvantages:**

• In counter type A/D converter, the conversion time is very long, variable and proportional to the amplitude of the analog input voltage. Since the counter always counts from 0 through a normal sequence, a maximum of  $2^n$  counts are required to convert a full-scale analog input voltage. Hence for an n-bit ADC,

the average conversion time is  $\frac{2^n}{2} = 2^{n-1}$  times the clock period, which can be very long for large value of n.

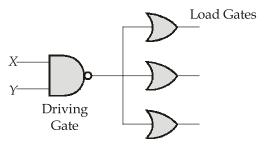

(ii) Fan Out: When the output of a logic gate is connected to one or more inputs of other gates, a load on the driving gate is created. There is a limit to the number of load gate inputs that a given gate can drive. This limit is called the fan out of the gate.

- 1. High state noise margin =  $V_{OH(min)} V_{IH(min)}$ = 2.7 - 2 = 0.7 V

- 2. Low state noise margin =  $V_{IL(max)}$   $V_{OL(max)}$ = 0.8 - 0.4 = 0.4 V

- 3. High state fan-out =  $\frac{I_{OH}}{I_{IH}} = \frac{400}{25} = 16$ Low state fan-out =  $\frac{I_{OL}}{I_{IL}} = \frac{8}{0.4} = 20$

Among these worst case fan-out will be taken, so number of NAND gate inputs that can be driven is 16.

### Q.7 (b) Solution:

(i)  $3441 + 4235 \over 7676$

Since largest digit used is 7, it is true for any base > 7

(ii)  $\frac{142}{7} = 16$

Assume base for the operation is b then

$$\frac{b^2 + 4b + 2}{7} = b + 6$$

$$b^{2} - 3b - 40 = 0$$

$$\Rightarrow \qquad \qquad b = 8$$

$$\therefore \qquad \text{base (b)} = 8$$

(iii)

$$23 + 44 + 14 + 32 = 223$$

Assume base for the operation is *b*

$$(2b+3) + (4b+4) + (b+4) + (3b+2) = (2b^2 + 2b + 3)$$

$$b^2 - 4b - 5 = 0$$

$$b = 5$$

(iv)

$$21 \times 16 = 366$$

Assume base for the operation is b then,

$$(2b+1) (b+6) = 3b^{2} + 6b + 6$$

$$2b^{2} + 13b + 6 = 3b^{2} + 6b + 6$$

$$b^{2} - 7b = 0$$

$$b = 7$$

$$302 = 12.1$$

(v)

$$\frac{302}{20} = 12.1$$

Assume base for operation is b,

$$\frac{3b^{2} + 2}{2b} = b + 2 + \frac{1}{b}$$

$$\frac{3b^{2} + 2}{2b} = \frac{b^{2} + 2b + 1}{b}$$

$$3b^{2} + 2 = 2b^{2} + 4b + 2$$

$$b^{2} - 4b = 0$$

$$b = 4$$

$$\sqrt{51} = 6$$

Assume base for the operation is b

$$5b + 1 = 36$$

$$5b = 35$$

$$b = 7$$

(vi)

## MADE ERSY

### Q.7 (c) Solution:

(i) Let  $H_M(e^{j\omega}) = |H(e^{j\omega})|$

The inverse DTFT of  $H_M(e^{j\omega})$  is given by,

$$h_{M}[n] = \frac{1}{2\pi} \int_{-\pi}^{\pi} H_{M}(e^{j\omega}) e^{j\omega n} d\omega$$

$$= \frac{1}{2\pi} \int_{-\pi/3}^{\pi/3} (1) e^{j\omega n} d\omega = \frac{1}{2\pi} \left[ \frac{e^{j\omega n}}{jn} \right]_{-\pi/3}^{\pi/3}$$

$$= \frac{1}{2\pi jn} \left[ e^{j\pi/3} - e^{-j\pi/3} \right] = \frac{\sin \pi/3}{\pi n}$$

If the group delay function,

$$\tau_g(\omega) = \frac{-d[H(e^{j\omega})]}{d\omega} = \alpha \text{ (where '}\alpha' \text{ is a constant)},$$

then

$$|H(e^{j\omega})| = -\alpha\omega + \beta$$

(where '\beta' is a constant).

Since the impulse response h[n] is real, the phase response  $H(e^{j\omega})$  is an odd function, and hence for  $H(e^{j\omega})$  to be an odd function, the constant  $\beta = 0$ .

Therefore,  $H(e^{j\omega}) = -\alpha\omega$

$$\Rightarrow H(e^{j\omega}) = |H(e^{j\omega})|e^{j|H(e^{j\omega})} = H_M(e^{j\omega})e^{-j\alpha\omega}$$

Taking the inverse DTFT, we obtain

$$h[n] = h_M(n - \alpha)$$

$$\Rightarrow h[n] = \frac{\sin\frac{\pi}{3}(n-\alpha)}{\pi(n-\alpha)}$$

Given that,  $\tau_g(\omega) = \frac{3}{2}$

$$\Rightarrow \frac{-d|H(e^{j\omega})|}{d\omega} = \frac{3}{2}$$

$$\Rightarrow \frac{-d}{d\omega}(-\alpha\omega) = \frac{3}{2}$$

$$\Rightarrow$$

$\alpha = \frac{3}{2}$

:. The real-valued impulse response of the filter is,

$$h[n] = \frac{\sin\frac{\pi}{3}\left(n - \frac{3}{2}\right)}{\pi\left(n - \frac{3}{2}\right)}$$

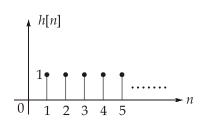

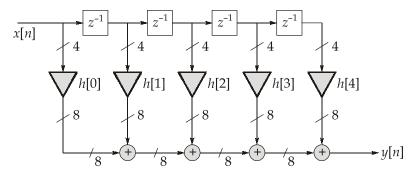

(ii) For a 5-coefficient FIR filter, if x[n] is the input sequence, the output sequence is given by:

$$y[n] = h[0] x[n] + h[1] x[n-1] + h[2] x[n-2] + h[3] x[n-3] + h[4] x[n-4]$$

Taking *z*-transform on both the sides,

$$Y(z) = h[0] X(z) + h[1] z^{-1} X(z) + h[2] z^{-2} X(z) + h[3] z^{-3} X(z) + h[4] z^{-4} X(z)$$

$$\therefore Y(z) = X(z) [h[0] + z^{-1}h[1] + z^{-2}h[2] + z^{-3}h[3] + z^{-4}h[4]]$$

The above FIR filter can be implemented using direct-form structure as shown below:

The input x[n] is available in 4-bit 2's complement representation, hence the input line is represented by a bus of 4-bit.

Assuming, the filter coefficients are also represented by 4 bits, the multiplier is then a  $4 \times 4$  bit fixed point arithmetic multiplier giving 8-bit output. The adder adds two 8-bit fixed point words and hence, a 8-bit adder is required.

The above structure, therefore requires:

- 1. 4-delay elements: Each delay element consists of 4-bit PIPO register which produces a delay of 1 clock cycle.

- 2. Five  $4 \times 4$  bit fixed point multipliers.

- 3. Four 8-bit adders.

## Q.8 (a) Solution:

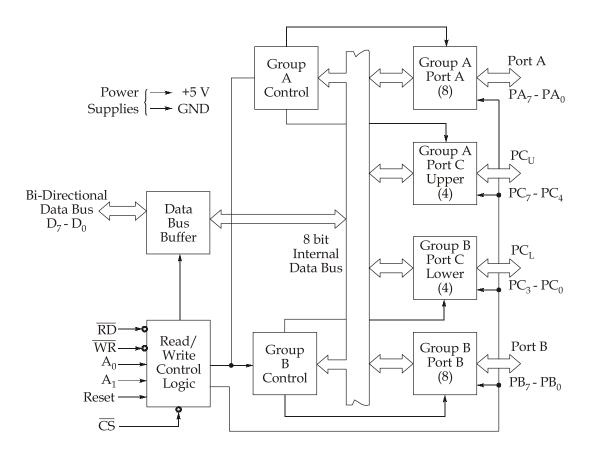

(i) Block diagram of 8255A

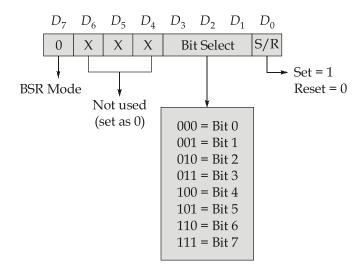

(ii) BSR mode is used to set or reset the bits of port C.

BSR mode in 8255A is concerned only with the eight bits of port C, which can be set or reset by writing an appropriate control word in the control register.

A control word with bit  $D_7$  = 0 is recognised as a BSR control word, and it does not alter any previously transmitted control word with bit  $D_7$  = 1; thus input-output operations of port A and port B are not affected by a BSR control word. In BSR mode, individual bits of port C can be used for applications such as an ON/OFF switch.

#### **BSR** control word:

56 I

(iii) The control word to set/reset the bits PC<sub>7</sub> and PC<sub>3</sub> can be obtained as below,

Given, the control register address = 83H.

#### **Subroutine:**

BSR: MVI A, 0FH; Load byte in accumulator to set PC<sub>7</sub>

OUT 83H ;  $PC_7$  set to 1

MVI A, 07H ; Load byte in accumulator to set PC<sub>3</sub>

OUT 83H;  $PC_3$  set to 1

CALL DELAY ; Delay

MVI A, 06H; Load byte in accumulator to reset PC<sub>3</sub>

OUT 83H; Reset  $PC_3$  to 0

MVI A, 0EH; Load byte in accumulator to reset PC<sub>7</sub>

OUT 83H; Reset  $PC_7$  to 0

**RET**

The delay program can be written as below:

DELAY: MVI B, FFH

LOOP : DCR B

JNZ LOOP

RET

#### Q.8 (b) Solution:

(i) Given, fundamental period, T = 3

The Fourier series coefficient of an even function is also even. Thus, From the fact 2, we can conclude that x(t) = x(-t)

We have,

$$a_k = \frac{1}{T} \int_0^T x(t) e^{-jk\frac{2\pi}{T}t}$$

From the fact 1,

$$a_k = a_{k+2}$$

then we require,

$$x(t) \cdot e^{-jk \times \frac{2\pi}{T}t} = x(t)e^{-j(k+2) \times \frac{2\pi}{T}t}$$

$$\Rightarrow$$

$$e^{j\frac{4\pi}{3}t} = 1 = e^{j2n\pi}$$

$$\Rightarrow$$

$$t = \frac{3n}{2}$$

, where  $n = 0, \pm 1, \pm 2, ...$

Thus, x(t) may have non-zero values only for t = 0,  $\pm 1.5$ ,  $\pm 3$ ,  $\pm 4.5$ ..... From the fact 3,

$$\int_{-0.5}^{0.5} x(t) dt = 1,$$

We may conclude that  $x(t) = \delta(t)$  for  $-0.5 \le t \le 0.5$ .

Also given  $\int_{0.5}^{1.5} x(t)dt = 2$ , thus we may conclude  $x(t) = 2\delta \left(t - \frac{3}{2}\right)$  in the range  $0.5 \le t \le 1.5$ .

(Impulse must be within the given range)

Therefore, the periodic signal x(t) with T = 3 can be written as,

$$x(t) = \sum_{k=-\infty}^{\infty} \delta(t-3k) + 2\sum_{k=-\infty}^{\infty} \delta\left(t-3k-\frac{3}{2}\right)$$

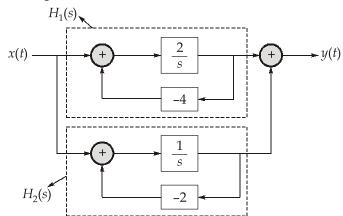

(ii) The given overall system may be treated as two feedback systems of the form shown below connected in parallel.

The transfer function of the upper feedback system is,

$$H_1(s) = \frac{\frac{2}{s}}{1+4\times\frac{2}{s}} = \frac{2}{s+8}$$

Similarly, the transfer function of the lower feedback system is,

$$H_2(s) = \frac{\frac{1}{s}}{1+2(\frac{1}{s})} = \frac{1}{s+2}$$

The transfer function of the overall system is

$$H(s) = H_1(s) + H_2(s)$$

$$= \frac{2}{s+8} + \frac{1}{s+2}$$

$$H(s) = \frac{3s+12}{s^2+10s+16}$$

. .

$$H(s) = \frac{Y(s)}{X(s)}$$

, we may write,

$$Y(s)[s^2 + 10s + 16] = X(s)[3s + 12]$$

$$s^2Y(s) + 10sY(s) + 16Y(s) = 3sX(s) + 12X(s)$$

Taking the inverse Laplace transform, we get the differential equation of the system as,

$$\frac{d^2y(t)}{dt^2} + 10\frac{dy(t)}{dt} + 16y(t) = 3\frac{dx(t)}{dt} + 12x(t)$$

## Q.8 (c) Solution:

State table of Moore-machine,

| Present State | Input<br>X | Next State | Output Z |

|---------------|------------|------------|----------|

| $q_0$         | 0          | $q_1$      | 0        |

| 70            | 1          | $q_2$      | 0        |

| $q_1$         | 0          | $q_1$      | 0        |

| 71            | 1          | $q_3$      | 1        |

| a-            | 0          | $q_4$      | 1        |

| $q_2$         | 1          | $q_2$      | 0        |

| a-            | 0          | $q_4$      | 1        |

| $q_3$         | 1          | $q_2$      | 0        |

| a.            | 0          | $q_1$      | 0        |

| $q_4$         | 1          | $q_3$      | 1        |

Here, the states  $q_1$  and  $q_4$  are equivalent and the states  $q_2$  and  $q_3$  are equivalent. So, reduced state table,

| <b>Present State</b> | Input<br>X | Next State | Output Z |

|----------------------|------------|------------|----------|

| $q_0$                | 0          | $q_1$      | 0        |

| 70                   | 1          | $q_2$      | 0        |

| $q_1$                | 0          | $q_1$      | 0        |

| 71                   | 1          | $q_2$      | 1        |

| $q_2$                | 0          | $q_1$      | 1        |

| 72                   | 1          | $q_2$      | 0        |

**Excitation table:** Let state  $q_0$  = 00,  $q_1$  = 01,  $q_2$  = 10

| <b>Present State</b> |       | Input | Next State      |                 | J-K FF Inputs |       |       |       | Output    |

|----------------------|-------|-------|-----------------|-----------------|---------------|-------|-------|-------|-----------|

| $Q_1$                | $Q_0$ | X     | $Q_1^{\dagger}$ | $Q_0^{\dagger}$ | $J_1$         | $K_1$ | $J_0$ | $K_0$ | $\bar{Z}$ |

| 0                    | 0     | 0     | 0               | 1               | 0             | Χ     | 1     | Χ     | 0         |

| 0                    | 0     | 1     | 1               | 0               | 1             | X     | 0     | X     | 0         |

| 0                    | 1     | 0     | 0               | 1               | 0             | X     | Χ     | 0     | 0         |

| 0                    | 1     | 1     | 1               | 0               | 1             | X     | Χ     | 1     | 1         |

| 1                    | 0     | 0     | 0               | 1               | X             | 1     | 1     | X     | 1         |

| 1                    | 0     | 1     | 1               | 0               | X             | 0     | 0     | X     | 0         |

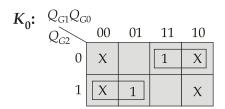

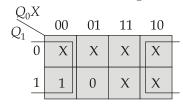

# K-Map for $J_1$ :

$$J_1 = X$$

## K-Map for $K_1$ :

$$K_1=\overline{X}$$

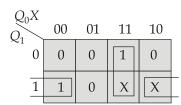

K-Map for  $J_0$ :

| $Q_0$ | X | 00 | 01 | 11 | 10 |

|-------|---|----|----|----|----|

| ~1    | 0 | 1  | 0  | Х  | X  |

|       | 1 | 1  | 0  | Χ  | X  |

$$J_0=\, \overline{X}$$

# K-Map for $K_0$ :

$$K_1 = X$$

# K-Map for output Z:

$$Z = Q_0 X + Q_1 \overline{X}$$

## **Circuit:**