## Q.No. 1 to Q.No. 10 carry 1 mark each

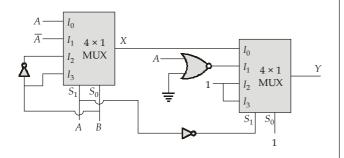

**Q.1** The value of *X* and *Y* is

$\begin{array}{l} (1110011.0011)_2 = (X)_8 = (Y)_{10} \\ (a) \ X = 163.14 \quad Y = 110.3 \\ (b) \ X = 163.14 \quad Y = 115.1875 \\ (c) \ X = 155.30 \quad Y = 110.3 \end{array}$

(d) X = 155.3 Y = 115.1875

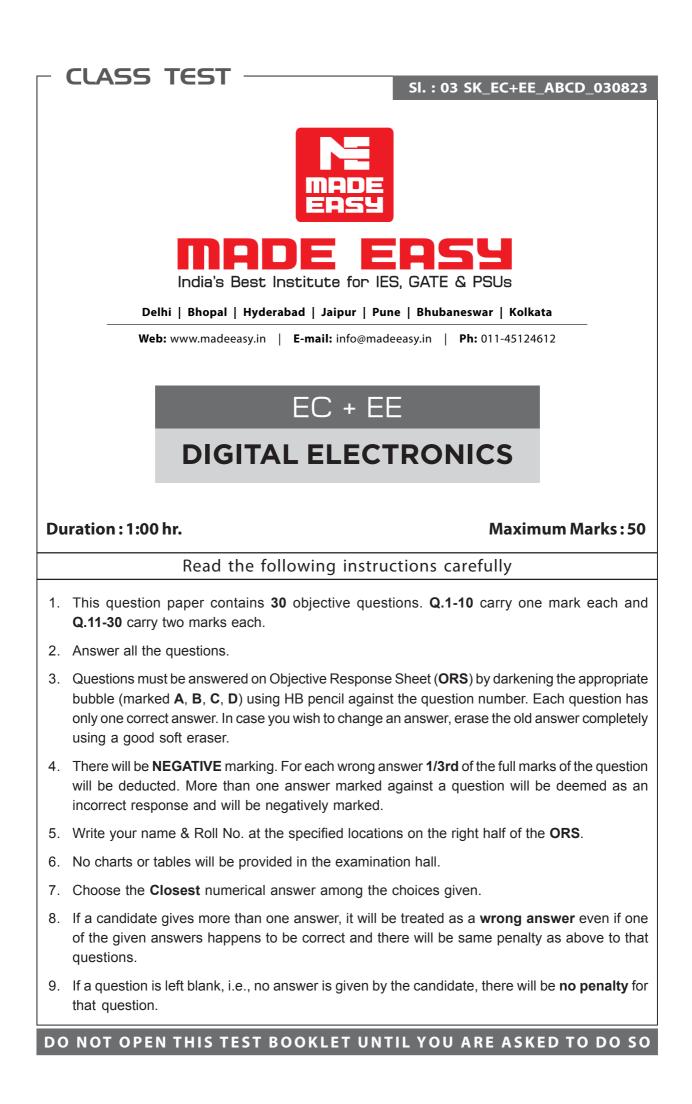

## Q.2 The output of the 4-bit comparator is

- (a) X = 1, Y = 0, Z = 0

(b) X = 0, Y = 1, Z = 0

(c) X = 1, Y = 0, Z = 1

- (d) X = 0, Y = 0, Z = 1

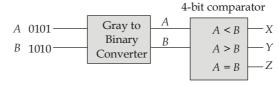

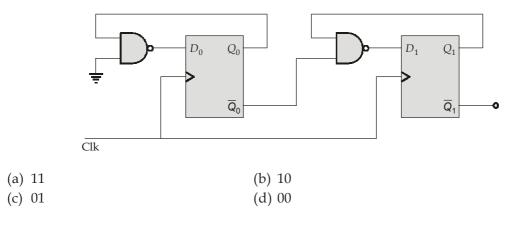

**Q.3** Identify the state of the flip-flops  $Q_2Q_1$  after 3 clock cycles if the initial state,  $Q_1Q_2 = 01$ .

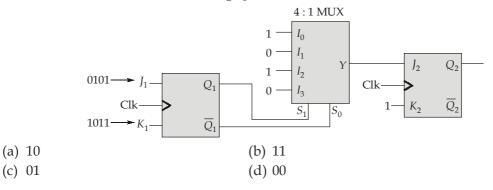

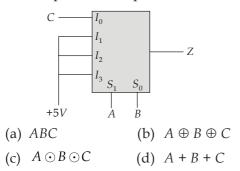

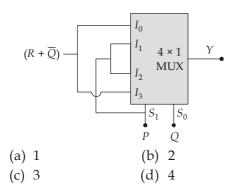

**Q.4** The final expression *Y* at the output of the MUX is

- **Q.5** The input clock frequency to an 8-bit successive approximation ADC is 5 MHz. The time required to convert 16 V analog input into equivalent digital output is

- (a) 0.5 µsec (b) 1 µsec

- (c) 1.6 µsec (d) 2.5 µsec

## India's Best Institute for IES, GATE & PSUs

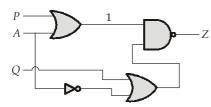

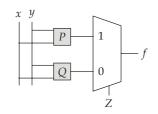

**Q.6** The circuit shown below is used the implement the function  $Z = f(A, B) = \overline{A} + B$ . The values of *P* and *Q* are:

- (a) P = A, Q = B (b) P = B,  $Q = \overline{A}$

- (c)  $P = \overline{B}, Q = 0$  (d)  $P = 0, Q = \overline{B}$

- **Q.7** A 4-bit ripple counter and 4-bit synchronous counter are made by flip-flops having propagation delay of 10 ns each. If the worst case delay in the ripple counter and the synchronous counter be *R* and *S* respectively then,

- (a) R = 10 ns, S = 40 ns

- (b) R = 40 ns, S = 10 ns

- (c) R = 10 ns, S = 30 ns

- (d) R = 30 ns, S = 10 ns

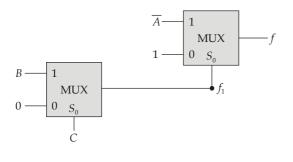

- **Q.8** The MUX shown below is 4 × 1 multiplexer. The output for an input of *A*, *B*, *C* will be

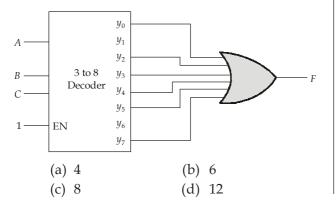

**Q.9** The circuit shown below represents a Boolean expression. Number of minterms present in the Boolean expression are

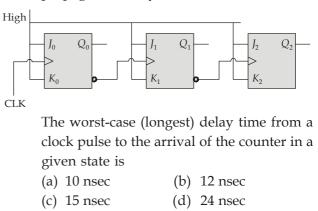

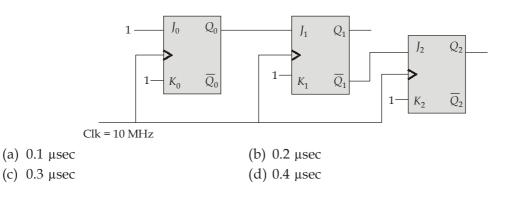

**Q.10** In the given counter, each flip-flop has a propagation delay of 8 ns.

Q.No. 11 to Q.No. 30 carry 2 marks each

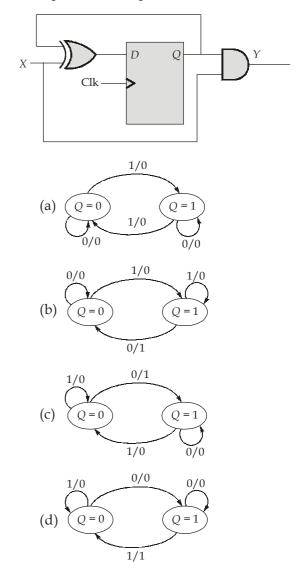

**Q.11** Which of the following represents the correct state diagram for circuit given with input *X* and output *Y*?

© Copyright: **MADE EASY**

Q.12 Consider the Boolean expression given below

$$Y = \overline{A\overline{B}C + \overline{\overline{A}B(C+D) + B\overline{C}}}$$

The simplified Boolean expression for Y is

- (a)  $\overline{A}\overline{B} + BC$  (b)  $A\overline{B} + \overline{B}C$

- (c)  $\overline{A}B + \overline{B}\overline{C}$  (d)  $\overline{A}B + B\overline{C}$

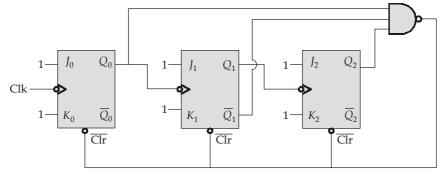

- **Q.13** Identify the type of asynchronous counter and the MOD number. Assume initial state  $Q_2Q_1Q_0$  to be 000.

- (a) Up-counter, MOD-3

- (b) Down-counter, MOD-5

- (c) Up-counter, MOD-5

(d) Down-counter, MOD-3

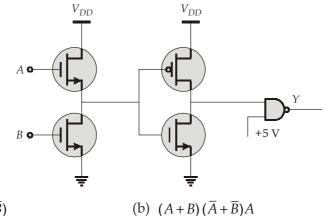

Q.14 The output *Y* can be represented by

(a)  $B(A+B)(\overline{A}+\overline{B})$ (b)  $(A+B)(\overline{A}+\overline{B})$ (c)  $(A+\overline{B})(\overline{A}+B)$ (d)  $(\overline{A}+\overline{B})(\overline{A}+B)$

**Q.15** In the circuit given below, initial state  $Q_0Q_1Q_2 = 000$ . The time taken by state  $Q_2Q_1Q_0$  to become 110 is

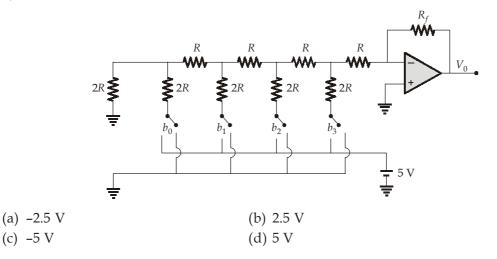

**Q.16** If the input to the ladder DAC is 1000. What is the value of output voltage  $V_0$  if  $R = 5 \text{ k}\Omega$  and  $R_f = 10 \text{ k}\Omega?$

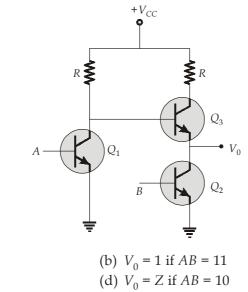

**Q.17** In the given circuit,  $V_0$  is the output, A and B are the inputs. The output can take the values 0, 1 and high impedance state (Z).

The output of the given circuit is

(a)  $V_0 = 0$  if AB = 00(c)  $V_0 = 1$  if AB = 10

**Q.19** The minimum number of 2-input NAND gates required to realise the minimized output expression *Y* of the given 4 × 1 MUX is

**Q.20** The propagation delay of  $4 \times 1$  MUX is 8 ns and delay of NOR and NOT gates is 2ns. For A = 1, B = 0 the output Y will be stable in

| (a) | 10 nsec | (b) | 5 nsec |

|-----|---------|-----|--------|

|     |         |     |        |

(c) 15 nsec (d) 20 nsec

- **Q.21** Assume Y = f(A, B, C, D) the Boolean expression  $Y = \Sigma m(1, 3, 7, 11, 15) + d(0, 2, 5)$  in its simplified form is given as,

- (a) CD + AB (b)  $CD + \overline{A}\overline{B}$

- (c)  $AC + \overline{B}\overline{D}$  (d) AC + BD

- Q.22 The network shown below implements:

- (a) NOR gate (b) NAND gate

- (c) XOR gate (d) XNOR gate

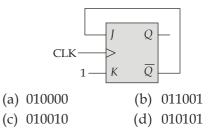

- **Q.23** The JK flip-flop shown below is initially cleared and then 5 clock pulses are applied, the sequence at the *Q* output will be

- Q.24 A full adder is realized using only 2 input NOR gates. The minimum number of NOR gates required to realize Sum and Carry out is

- (a) 8 (b) 9 (c) 10 (d) 12

- **Q.25** A 1-bit full-adder takes 20 ns to generate carry-out bit and 40 ns for the sum bit. The maximum rate of addition per second, when four 1-bit full adders are cascaded is (a)  $10 \times 10^6$  (b)  $10 \times 10^4$ (c)  $5 \times 10^6$  (d)  $5 \times 10^4$

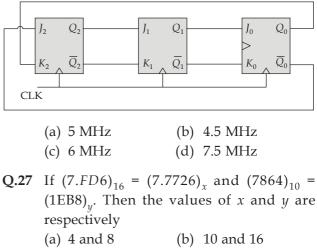

- **Q.26** The three stage Johnson counter as shown in figure below is clocked at a constant frequency of 15 MHz from the starting state of  $Q_2 Q_1 Q_0 = 101$ . The frequency of output  $Q_2 Q_1 Q_0$  will be

(c) 8 and 16 (d) 8 and 8

## India's Beet Institute for IES, GATE & PSUs

Q.28 The minimized expression for the Boolean function

$$f(A, B, C, D) = \Sigma m (0, 2, 3, 4, 6, 8, 10, 11)$$

(a)

$$\overline{A}\overline{D} + \overline{B}D + \overline{B}C$$

(b)  $\overline{A}\overline{D} + B\overline{D} + B\overline{C}$

- (c)  $\overline{A}\overline{D} + \overline{B}\overline{D} + BC$  (d)  $\overline{A}\overline{D} + \overline{B}\overline{D} + \overline{B}C$

- **Q.29** The majority function is a Boolean function f(x, y, z), that takes the value 1 whenever a majority of variables x, y, z are 1. In the circuit diagram for the majority function shown below. The logic gates for the boxes labeled P and Q are, respectively

(a) AND, OR(b) OR, AND(c) EXOR, OR(d) EXOR, AND

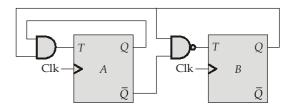

Q.30 The circuit shown in figure below is,

Initially both flip-flops are at 00. After two clock pulses, the content at  $Q_A Q_B$  is

| (a) 00 | (b) 01 |  |

|--------|--------|--|

| (c) 10 | (d) 11 |  |

© Copyright: **MADE EASY**