S.No.: 04 LS1\_EE\_T\_230819

**Digital Electronics**

# MADE ERSY

India's Best Institute for IES, GATE & PSUs

Delhi | Noida | Bhopal | Hyderabad | Jaipur | Lucknow | Indore | Pune | Bhubaneswar | Kolkata | Patna

Web: www.madeeasy.in | E-mail: info@madeeasy.in | Ph: 011-45124612

# CLASS TEST 2019-2020

# **ELECTRICAL ENGINEERING**

# **Digital Electronics**

Date of Test: 23/08/2019

|    |     |     |     | Answer Key |         |         |

|----|-----|-----|-----|------------|---------|---------|

| 1. | (d) | 7.  | (b) | 13. (d)    | 19. (c) | 25. (a) |

| 2. | (b) | 8.  | (*) | 14. (c)    | 20. (b) | 26. (a) |

| 3. | (c) | 9.  | (d) | 15. (c)    | 21. (d) | 27. (a) |

| 4. | (a) | 10. | (a) | 16. (a)    | 22. (a) | 28. (c) |

| 5. | (d) | 11. | (a) | 17. (a)    | 23. (a) | 29. (a) |

| 6. | (b) | 12. | (a) | 18. (a)    | 24. (b) | 30. (d) |

# **DETAILED EXPLANATIONS**

# 1. (d)

Given 12 bit content in excess 3 form

$$1000\ 1001\ 0111 = 897 - 333 = 564$$

#### 3. (c)

Dual of Ex-OR is Ex-NOR. Also, complement of Ex-OR is Ex-NOR whihe is dual of Ex-OR.

## 4. (a)

| CLK | State | Serial in |

|-----|-------|-----------|

| Χ   | 0011  | 0         |

| 1   | 0001  | 1         |

| 2   | 1000  |           |

## 5. (d)

Output of stage 1  $X \oplus X = 0$ Output of 2nd stage 1  $\oplus$  0 = 1 Output Y = 1  $\oplus$  0 = 1

# 6. (b)

Minimum number of FF required,

$$2^n \ge \text{Mod no.}$$

$$2^n \ge 128$$

$$n = 7$$

$$\overline{(A \cdot \overline{B} + \overline{C})D + \overline{E}}$$

$$\overline{(A \cdot \overline{B} + \overline{C})D} \cdot E$$

$$(\overline{(A \cdot \overline{B} + \overline{C})} + \overline{D}) E$$

$$((\overline{A \cdot \overline{B}} \cdot C) + \overline{D})E$$

$$((\bar{A} + B) \cdot C + \bar{D})E$$

# 9. (d)

$$(1010) = 10_{10}$$

gives 3 V

Step size =

$$\frac{3V}{10}$$

= 0.3 V

Output voltage fof 0100 =

$$(=4_{10})$$

is =  $4 \times 0.3 = 1.2$  V

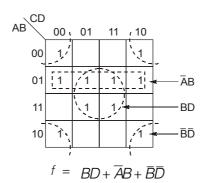

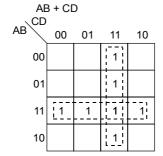

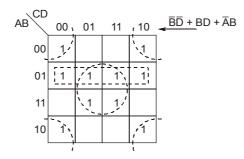

k map

*:*.

' = BD + AE

# 11. (a)

| $A_3$                              | $A_2$                              | $A_1$       | $A_0$       | у                     |

|------------------------------------|------------------------------------|-------------|-------------|-----------------------|

| A <sub>3</sub> 0 0 0 0 0 0 0 0 0 0 | A <sub>2</sub><br>0<br>0<br>0<br>0 | 0           | 0           | 0                     |

| 0                                  | 0                                  | 0<br>0<br>1 | 1           | 0<br>0<br>0<br>1      |

| 0                                  | 0                                  | 1           | 0           | 0                     |

| 0                                  | 0                                  | 1           | 1           | 1                     |

| 0                                  | 1                                  | 0           | 0           | 1                     |

| 0                                  | 1                                  | 0           | 1           | 1                     |

| 0                                  | 1                                  | 1           | 0           | 1                     |

| 0                                  | 1                                  | 1           | 1           | 1                     |

| 1                                  | 0<br>0<br>0                        | 0<br>0<br>1 | 0           | 0                     |

| 1                                  | 0                                  | 0           | 1           | 0                     |

| 1                                  | 0                                  | 1           | 0           | 0                     |

| 1                                  | 0                                  | 1           | 1           | 0                     |

| 1                                  | 1                                  | 0           | 0           | 0                     |

| 1                                  | 1                                  | 0           | 0<br>1<br>0 | 0<br>0<br>0<br>0<br>0 |

| 1                                  | 1                                  | 1           | 0           |                       |

| 1                                  | 1                                  | 1           | 1           | 0                     |

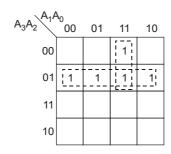

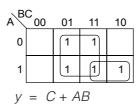

k-map simiplification

$$y = \overline{A}_3 A_2 + \overline{A}_3 A_1 A_0 = \overline{A}_3 (A_2 + A_1 A_0)$$

# 12. (a)

$$x = (M+N)(\overline{M}+P)(\overline{N}+\overline{P})$$

$$= (M\overline{M}+MP+N\overline{M}+NP)(\overline{N}+\overline{P})$$

$$= (MP+N\overline{M}+NP)(\overline{N}+\overline{P})$$

$$= (MP+N\overline{M}+NP)(\overline{N}+\overline{P})$$

$$= MP\overline{N}+MP\overline{P}+N\overline{M}\overline{N}+N\overline{M}\overline{P}+NP\overline{N}+NP\overline{D}$$

$$x = MP\overline{N}+N\overline{M}\overline{P}$$

# 13. (d)

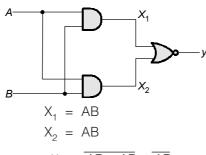

$$y = \overline{AB + AB} = \overline{AB}$$

| А | В | $y = \overline{AB}$ |                  |

|---|---|---------------------|------------------|

| 0 | 0 | 1                   |                  |

| 0 | 1 | 1                   |                  |

| 1 | 0 | 1                   |                  |

| 1 | 1 | 0                   | → LED will be ON |

|   |   |                     |                  |

# 14. (c)

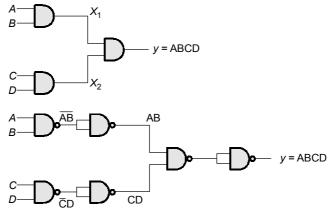

Implementing y suing 2 input AND gates

: Hence total 6, 2 input NAND gates are required.

# 15. (c)

The expression of output is

$$r = \left(\overline{A} + B\right)\left(A + \overline{B}\right) = A\overline{A} + \overline{A}\overline{B} + AB + B\overline{B} = AB + \overline{A}\overline{B} = A \odot B$$

# 16. (a)

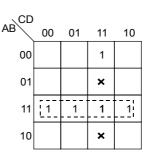

k-map

Comparing both the k-maps, it to clear that there are two don't care enteries. Which are (7, 11).

Drawing k-map for x.

$$x = (A + C + D)(\overline{A} + \overline{C} + D)(A + \overline{B})$$

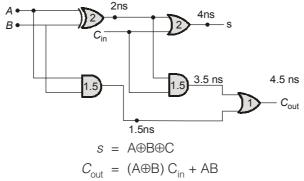

#### 18. (a)

*:*.

Full adder implementation

From figure, it is clear that delay for sum and carry will be 4ns and 4.5ns respectively.

#### 19. (c)

4 bit ripple ripple counter has  $2^4 = 16$  states

5 bit ring counter has 5 states

BCD counter has 10 states

5 bit Jhonson counter has  $5 \times 2 = 10$  states

#### 21. (d)

Propagation delay

$$T_d = (n-1) t_{p \text{ carry}} + \max (t_{p \text{ carry}}, t_{p \text{ sum}})$$

=  $(16-1) \times 5 + \max (5.6)$

=  $75 + 6 = 81 \text{ ns}$

For given quadratic equation,

$$(x-3) = 0$$

and

$$(x-6) = 0$$

will be two factors

*:*.

$$(x-3)(x-6) = x^2 - 11x + 22$$

both are equal

$$x^2 - (6 + 3)x + 6 \times 3 = x^2 - 11x + 22$$

Let b be the base of number

$$6 + 3 = 1b + 1$$

$$b = 8$$

Also,

$$6 \times 3 = 2b + 2$$

$$18 = 2b + 2$$

$$b = 8$$

# 23. (a)

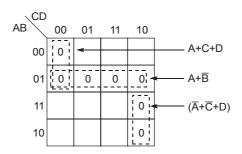

k map

#### 24. (b)

Let n number of flip flop cascaded each having propagation delay of  $t_{pd}$ . Frequency of operation

$$\frac{1}{nt_{nd}} \ge 10 \,\mathrm{MHz}$$

*:*.

$$n \le \frac{1}{t_{pd} \times 10 \text{ MHz}} \le \frac{1}{12 \times 10^{-9} \times 10^7} \le \frac{100}{12}$$

$$n = 8$$

For n = 8 MOD number of counter  $2^8 = 256$

## 25. (a)

When odd number of NOT gate are arranged with output as a feedback to input it acts as an oscillator with frequency,

$$f = \frac{1}{2nt_{pd}}$$

$n = \text{Number of NOT gates}$

*:*.

$$f = \frac{1}{2 \times 5 \times t_{pd}}$$

··

$$t_{pd} = \frac{1}{10 \times f_{max}} = \frac{1}{10 \times 20} \,\mu \,\text{s} = \frac{1000}{10 \times 20} \,\mu \,\text{s} = 5 \,\text{ns}$$

: Each NOT gate has a propagation delay of 5 ns.

Expression of E.

$$E = \overline{A}O + A \cdot B = AB$$

$$y = \overline{E}C + E \cdot 1 = \overline{AB}C + AB$$

$$= (\overline{A} + \overline{B})C + AB = \overline{A}C + \overline{B}C + AB$$

k-map simplification

## 27. (a)

An eight bit binary ripple counter will be RESET i.e. initial condition 00000000 after

∴ i.e. after 129 clock pulses counter will be at (00)<sub>10</sub>.

After additional (135 - 129) = 6 pulses counter will be at 0000 0110 state.

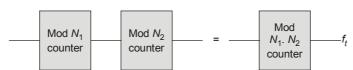

# 28. (c)

(i) n bit Johnson counter will have 2n states

$\therefore$  3bit Johnson counter has mod number =  $3 \times 2 = 6$

In 2nd stage, D -Fup flop acts as a T-flip flop and has mod no. 2

Hence given counter arrangement has  $6 \times 2 = 12 \mod \text{number}$

#### 29. (a)

Full scale voltage = Step size × Maximum count

= Step size ×

$$(2^n - 1)$$

= 10 mV × 255

= 2.55 V

% Resolution =  $\frac{1}{2^n - 1}$  × 100 =  $\frac{100}{255}$  = 0.392%

#### 30. (d)

Number of function using n variables is  $2^{2^n}$ .

Since, here n = 3, so number of function is 256.