|                                                                                                                                                                                           | LASS                 | 5 TE                              | ST –              |                               |                          | SI.:                        | : 02 SK_C               | S_ABCD_               | _090623    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------|-------------------|-------------------------------|--------------------------|-----------------------------|-------------------------|-----------------------|------------|

| Delhi       Bhopal       Hyderabad       Jaipur       Pune       Bhubaneswar       Kolkata         Web:       www.madeeasy.in       E-mail:       info@madeeasy.in       Ph: 011-45124612 |                      |                                   |                   |                               |                          |                             |                         |                       |            |

| COMPUTER ORGANIZATION                                                                                                                                                                     |                      |                                   |                   |                               |                          |                             |                         |                       |            |

|                                                                                                                                                                                           |                      | CC                                | OMPL              | JTER                          | SCIE                     |                             | E & I                   | Г                     |            |

|                                                                                                                                                                                           | _                    | СС                                |                   |                               | SCIE<br>st:09/0          |                             |                         | Γ                     |            |

| ANS                                                                                                                                                                                       | SWER K               |                                   |                   |                               |                          |                             |                         | Γ                     |            |

| <b>AN</b><br>1.                                                                                                                                                                           | <b>SWER K</b><br>(d) |                                   |                   |                               |                          |                             |                         | Γ<br>25.              | (c)        |

|                                                                                                                                                                                           |                      | ΈY >                              | Date              | e of Tes                      | st:09/(                  | 06/202                      | 23                      |                       | (c)<br>(b) |

| 1.                                                                                                                                                                                        | (d)                  | ΈΥ ➤<br>7.                        | Date<br>(d)       | e of Tes                      | s <b>t : 09/(</b><br>(a) | D6/2O2                      | 2 <b>3</b><br>(b)       | 25.                   |            |

| 1.<br>2.                                                                                                                                                                                  | (d)<br>(a)           | <b>ΈΥ &gt;</b><br>7.<br>8.        | (d)<br>(c)        | e of Tes<br>13.<br>14.        | (a)<br>(b)               | 06/202<br>19.<br>20.        | 23<br>(b)<br>(c)        | <br>25.<br>26.        | (b)        |

| 1.<br>2.<br>3.                                                                                                                                                                            | (d)<br>(a)<br>(a)    | <b>′EY &gt;</b><br>7.<br>8.<br>9. | (d)<br>(c)<br>(b) | e of Tes<br>13.<br>14.<br>15. | (a)<br>(b)<br>(a)        | 06/202<br>19.<br>20.<br>21. | 23<br>(b)<br>(c)<br>(d) | <br>25.<br>26.<br>27. | (b)<br>(c) |

# **DETAILED EXPLANATIONS**

## 1. (d)

- Since, vertical microprogram encode the control signals hence a signal decoder is needed which decrease the operation speed of vertical micro-programming in comparison with horizontal micro-programming.

- Since, the control signal bits under horizontal microprogram control unit are not encoded. Hence no signal decoder is needed.

#### 2. (a)

Since, it uses horizontal micro-programmed that requires 1 bit control / signal. For 125 control signal, we need 125 bits. Total number of micro-operation instruction =  $215 \times 6 = 1290$ It requires 11 bit.

# 3. (a)

A vectored interrupt is the one, where CPU actually knows the address of the ISR in advance, with the help of an interrupt vector, the interrupting device supplies the branch information to the processor.

#### 4. (c)

Address format

|        | <u>→</u> |         |

|--------|----------|---------|

| Opcode | Address  | Address |

| 6      | 5        | 5       |

Number of operations =  $2^6 = 64$ Number of free opcodes after 2-address = 64 - 2 = 62Number of 1 add instruction =  $62 \times 32 = 1984$ Free opcodes = 1984 - 1024 = 960Number of 0 add instruction =  $960 \times 32 = 30720$

#### 5. (b)

- More than one word are put in one cache block to explicit in the spatial locality of reference.

- By the help of virtual memory, programs can exceed from the size of primary memory, hence increases the degree of multi programming.

- Increasing RAM will result in fewer page faults.

Hence only  $\mathrm{S}_{\mathrm{2}}$  is the correct statement.

## 6. (c)

| Multiplier | Pair with $(q - 1)$ | Recorder |

|------------|---------------------|----------|

| 0          | 0                   | 0        |

| 1          | 0                   | -1       |

| 1          | 1                   | 0        |

| 0          | 1                   | +1       |

| 1          | 0                   | -1       |

| 0          | 1                   | +1       |

| 0          | 0                   | 0        |

| 1          | 0                   | -1       |

| 0          | 1                   | +1       |

| 1          | 0                   | -1       |

| 1          | 1                   | 0        |

| 0          | 1                   | +1       |

# India's Best Institute for IES, GATE & PSUs

7. (d)

**RAW hazards:**  $I_1 - I_2$ ,  $I_1 - I_4$ ,  $I_2 - I_3$ ,  $I_2 - I_4$ ,  $I_2 - I_5$ WAW hazards:  $I_2 - I_4$ WAR hazards:  $I_3 - I_4$  and  $I_2 - I_4$

8. (c)

Rate of transfer to or from any one disk = 30 MBps.

Maximum memory transfer rate =  $\frac{4 \text{ B}}{10 \times 10^{-9}} = 400 \times 10^{6} \text{Bps} = 400 \text{ MBps}$

Since rate of data transfer = 30 MBps

Here number of disk transfer =  $\left\lceil \frac{400}{30} \right\rceil$  = 13

Therefore, 13 disks can simultaneously transfer data to or from the main memory.

9. (b)

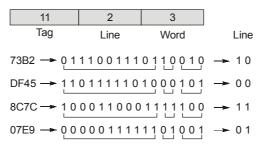

The address division will be given as:

## 10. (c)

- In pipelined CPU, there will be buffer delays. So, for single instruction non-pipelined CPU takes less time compared to pipelined CPU.

- Structural dependencies cause hazards during pipelining.

# 11. (a)

## For non-pipelined processor:

For p-instruction execution time =  $\frac{(p \times 5)}{5} = p$  ns

## Pipelined processor:

For *p*-instruction execution time =  $\frac{p}{3} = 0.33p$  ns

Speed-up =

$$\frac{p}{0.33p}$$

= 3.03

## 12. (b)

Memory mapped I/O uses the same address bus to address both memory and I/O devices the memory and registers of the I/O devices are mapped to address values.

So, when an address is accessed by the CPU, it may refer to a portion of physical RAM, but it can also refer to memory of I/O device.

# 13. (a)

| Number of lines | $= \frac{64K}{32} = 2^{1}$                | 1                |                             |

|-----------------|-------------------------------------------|------------------|-----------------------------|

| Number of sets  | $= \frac{2^{11}}{4} = \frac{2^{11}}{2^2}$ | = 2 <sup>9</sup> |                             |

|                 |                                           | — 32 bits —      |                             |

|                 | Tag                                       | SO               | WO                          |

|                 | 18 bits                                   | $\log_2 2^9 = 9$ | log <sub>2</sub> 32 = 5 bit |

| Tag memory size | $= S \times P \times #$                   | tag bits         |                             |

|                 | $= 2^9 \times 4 \times (2^{10})$          | 18 + 1 + 1 +     | 2)                          |

|                 | $= 2^9 \times 2^2 \times 2^2$             | 22 bits          |                             |

|                 | $= 2^{10} \times 2 \times$                | 22 bits          |                             |

|                 | = 44 K bits                               |                  |                             |

# 14. (b)

Programmed I/O: Processor issues an I/O command, on behalf of a processor, to an IO module; that process then busy-waits for the operation to be completed before proceeding.

Interrupt driven I/O: The processor issues an IO command on behalf of a process, continues to execute subsequent instruction, and is interrupted by the IO module when the latter has completed its work.

Direct memory access: A DMA module controls the exchange of data between main memory and IO

#### 15. (a)

module.

Number of interupts generated = 5000 interrupt / sec Time by 1 interrupt = 200  $\mu$ sec Time consumed by every interrupt = 250  $\mu$ s Fraction of processor time consumed = 200/250 = 0.8 In % = 0.8 × 100 = 80

# 16. (c)

Speedup (S) =

$$\frac{1}{(1-\text{Cache \% used}) + \left[\frac{\text{Cache \% used}}{\text{Speedup using cache}}\right]}$$

$$= \frac{1}{(1-F) + \left(\frac{F}{S}\right)} = \frac{1}{(1-0.9) + \left(\frac{0.9}{30}\right)} = \frac{1}{(0.1) + \left(\frac{0.9}{30}\right)}$$

$$= \frac{30}{3.9} = 7.69$$

## 17. (b)

|                | Instruction                            | Instruction size | Location  |

|----------------|----------------------------------------|------------------|-----------|

| I <sub>1</sub> | Load r <sub>0</sub> , 300              | 2 word           | 2000-2003 |

| I <sub>2</sub> | MOV r <sub>1</sub> , 5000              | 2 word           | 2004-2007 |

| I <sub>3</sub> | MOV r <sub>2</sub> , (r <sub>1</sub> ) | 1 word           | 2008-2009 |

| $I_4$          | Add r <sub>0</sub> , r <sub>2</sub>    | 1 word           | 2010-2011 |

| $I_5$          | MOV, 6000, r <sub>0</sub>              | 2 word           | 2012-2015 |

| I <sub>6</sub> | HALT                                   | 1 word           | 2016-2017 |

#### : Since 1 word is of 2 bytes.

If an interrupt occurs, the CPU has been halted after executing the HALT instruction, the return address 2016 is saved in the stack.

## 18. (b)

$$\begin{split} \mathsf{T}_{\text{avg}} &= \mathsf{h}_1 \, \mathsf{t}_1 + (1-\mathsf{h}_1) \mathsf{h}_2 \, (\mathsf{t}_2 + \mathsf{t}_1) + (1-\mathsf{h}_1) \, (1-\mathsf{h}_2) \, (\mathsf{t}_3 + \mathsf{t}_2 + \mathsf{t}_1) \\ &= 0.65 \times 0.02 + 0.35 \times 0.45 \times 0.22 + 0.35 \times 0.55 \times 2.22 \\ &= 0.013 + 0.03465 + 0.42735 \\ &= 0.475 = 475 \, \mu \text{sec} \end{split}$$

#### 19. (b)

Biased exponent = 18 + 64 = 82

Representing 82 in binary

$$(82)_2 = (1010010)_2$$

Representing mantissa in binary

$$(0.625)_{10} = (0.10100000)$$

Floating point representation is as follows:

| Sign bit | Exponent  |   |   |          | Mantissa |  |

|----------|-----------|---|---|----------|----------|--|

| 0        | 10,1001,0 |   |   | 10100000 |          |  |

|          | 5         | 2 | ŀ | ł        | 0        |  |

#### 20. (c)

| Instruction    | 1  | 2  | 3  | 4     | 5    | 6      | 7     | 8  | 9  | 10 | 11 | 12 | 13 |

|----------------|----|----|----|-------|------|--------|-------|----|----|----|----|----|----|

| I <sub>1</sub> | FI | DI | FO | EI    | WO   |        |       |    |    |    |    |    |    |

| I <sub>2</sub> |    | FI | DI | FO    | EI   | WO     |       |    |    |    |    |    |    |

| I <sub>3</sub> |    |    | FI | DI    | FO   | EI     | WO    |    |    |    |    |    |    |

| I <sub>4</sub> |    |    |    | FI    | DI   | FO     | EI    |    |    |    |    |    |    |

| I <sub>5</sub> |    |    |    |       | FI   | DI     | FO    |    |    |    |    |    |    |

| I <sub>6</sub> |    |    |    |       |      | FI     | FO    |    |    |    |    |    |    |

| I <sub>7</sub> |    |    |    |       |      |        | FI    | DI | FO | EI | WO |    |    |

| I <sub>8</sub> |    |    |    |       |      |        |       | FI | DI | FO | EI | WO |    |

| I <sub>9</sub> |    |    |    |       |      |        |       |    | FI | DI | FO | EI | WO |

|                |    |    | То | tal = | 13 * | 12 = 1 | 156 n | s  |    |    |    |    |    |

#### 21. (d)

Instruction : "Load 1000"

**Direct Addressing Mode:** Since the content of location '1000' is '1300'. Hence, 1300 will be loaded. **Indirect Addressing Mode:** The content of location '1000' is '1300'. The content of memory location '1300' is '1200'. Hence, 1200 will be loaded.

Base (Indexed) Addressing Mode:  $[1000 + 200] \Rightarrow [1200]$ . The content of memory location '1200' is 800.

# 22. (b)

Vertical Microprogramming :

## 23. (a)

24.

Assume *x* % of instructions incur 3 stall cycles.

Speedup =

$$\frac{\text{Pipeline depth}}{(1 + \#\text{stall/Instruction})}$$

Number of stall / Instructions= (% Instruction don't incur stall × 0 + % Instruction incur stall × 3)

=  $(1 - x) \times 0 + x (3) = 3x$

$\therefore$   $3 = \frac{5}{1 + 3x}$

$3 + 9x = 5$

$9x = 5 - 3 = 2$

$x = 2/9 = 0.222$

In % =  $0.222 \times 100 = 22.2$

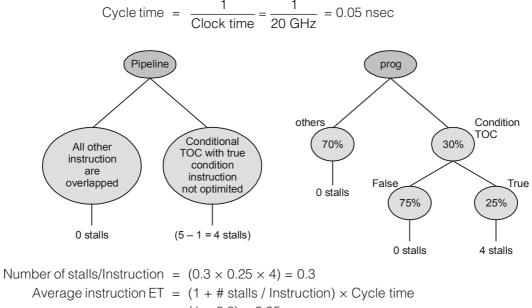

(a)

=  $(1 + 0.3) \times 0.05$  ns

= 0.065 ns

# India's Best Institute for IES, GATE & PSUs

#### 25. (c)

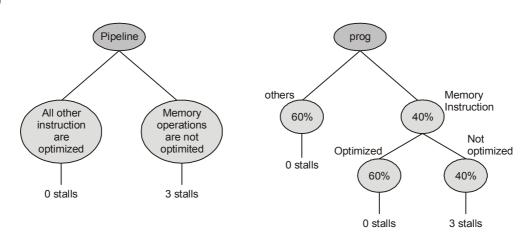

Number of stalls/Instruction =  $(0.4 \times 0.4 \times 3) = 0.48$

Average instruction ET =  $(1 + \# \text{ stalls / Instruction}) \times \text{Cycle time} = (1 + 0.48) \times 8 \text{ ns} = 11.84 \text{ ns}$

#### 26. (b)

| Sta      | ck                                            | k Accumulator |        | Register | -Memory                                 | Load-store     |                                                      |            |

|----------|-----------------------------------------------|---------------|--------|----------|-----------------------------------------|----------------|------------------------------------------------------|------------|

| Push (A) | 8 + 64                                        | Load A        | 8 + 64 |          | Load R <sub>1</sub> , A                 | 8 + 6 + 64     | Load R <sub>1</sub> , A                              | 8 + 6 + 64 |

| Push (B) | 8 + 64                                        | Add B         | 8 + 64 |          | Add R <sub>3</sub> , R <sub>1</sub> , B | 8 + 6 + 6 + 64 | Load R <sub>2</sub> , B                              | 8 + 6 + 64 |

| Add      | 8                                             | Store C       | 8 + 64 |          | Store R <sub>3</sub> , C                | 8 + 6 + 64     | Add R <sub>3</sub> , R <sub>1</sub> , R <sub>2</sub> | 8+6+6+6    |

| Pop (C)  | 8 + 64                                        |               |        |          |                                         |                | Store R <sub>3</sub> , C                             | 8 + 6 + 64 |

| = ;      | = 224 bits = 216 bits = 240 bits = 260 bits   |               |        |          |                                         |                |                                                      | = 260 bits |

|          | Total size = 224 + 216 + 240 + 260 = 940 bits |               |        |          |                                         |                |                                                      |            |

#### 27. (c)

251 opcodes  $\Rightarrow$  8 bits for each register

$\therefore$  Opcode  $R_1, R_2, R_3, R_4$

8 bits + 5 × 4 bits = 8 + 20 = 28 bits [:: 4 for 4 registers i.e.,  $R_1, R_2, R_3, R_4$ ].

#### 1. 0

# 28. (d)

Format of single precision floating point is

| ļ |       | 32 bits                                                                                                                                             | >             |

|---|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|   | S     | Exponant                                                                                                                                            | Mantissa      |

|   | 1 bit | 8 bits                                                                                                                                              | 23 bits       |

|   | 0     | 10000111                                                                                                                                            | 1010000000000 |

|   | =     | $1.M \times 2^{E-127}$<br>1.1010 × 2 <sup>135 - 127</sup><br>(1.1010) <sub>2</sub> × 2 <sup>8</sup><br>1.625 × 2 <sup>8</sup> = (416) <sub>10</sub> |               |

| n | 8     | 416                                                                                                                                                 |               |

Octal representation

Octal representation is (640).

# 29. (a)

Number of registers in RISC = G + W (L + C)208 = G + 16 (8 + 4)G = 16

#### 30. (c)

#### When instruction is a computation:

Memory reference : Fetch instruction Fetch reference of the operand Fetch operand

Total 3 memory references.

#### When instruction is a branch:

Memory reference : Fetch instruction

Fetch operand reference and loading program counter

Total 2 memory references.