# RANK IMPROVEMENT BATCH ELECTRONICS ENGINEERING

# **RIB-W** | **T1**

Session 2019 - 20 | S.No. : 220619\_LS1

| ANSW | ER KEY | > | Dig | gital E | lectronics |     |     |     |     |     |

|------|--------|---|-----|---------|------------|-----|-----|-----|-----|-----|

| 1.   | (b)    |   | 7.  | (b)     | 13.        | (a) | 19. | (c) | 25. | (b) |

| 2.   | (c)    |   | 8.  | (b)     | 14.        | (b) | 20. | (d) | 26. | (c) |

| 3.   | (b)    |   | 9.  | (d)     | 15.        | (a) | 21. | (b) | 27. | (a) |

| 4.   | (d)    |   | 10. | (b)     | 16.        | (b) | 22. | (c) | 28. | (c) |

| 5.   | (c)    |   | 11. | (a)     | 17.        | (c) | 23. | (c) | 29. | (c) |

| 6.   | (c)    |   | 12. | (d)     | 18.        | (b) | 24. | (c) | 30. | (b) |

# **DETAILED EXPLANATIONS**

#### 1. (b)

Overall MOD =  $3 \times 4 \times 5 = 60$ Lowest frequency is output frequency

$$f_{\rm out} = \frac{24 \times 10^6}{60} = 400 \,\rm kHz$$

2. (c)

Master slave configuration stores 1-bit of data.

3. (b)

It is a toggle flip-flop, the values toggle  $Q: 0 \rightarrow 1 \rightarrow 0 \rightarrow 1 \rightarrow 0 \rightarrow 1$   $\uparrow$ initial state

# 4. (d)

Excitation table

## 5. (c)

Using POS form

$$Z = (A+B+\overline{C})(\overline{A}+\overline{B}+\overline{C})$$

$$= (A+B)(\overline{A}+\overline{B})+\overline{C}$$

$$= A \oplus B + \overline{C}$$

$$= \overline{C} + (A \oplus B)$$

$$\overline{Y} = A + B + C$$

$$Y = \overline{A + B + C} = \overline{A}\overline{B}\overline{C}$$

$$= \Sigma m(0)$$

$$= \Pi M (1, 2, 3, 4, 5, 6, 7)$$

$$x \oplus y \oplus xy = (\overline{x}y + x\overline{y}) \oplus xy$$

$$= (\overline{x}y \oplus xy) + (x\overline{y} \oplus xy)$$

$$= y(x \oplus \overline{x}) + x(y \oplus \overline{y})$$

$$= y + x$$

8. (b)

$$Y = I_0 \cdot \overline{S}_1 \overline{S}_0 + I_1 \cdot \overline{S}_1 S_0 + I_2 \cdot S_1 \overline{S}_0 + I_3 S_1 S_0$$

$$Y = A\overline{B} + (1)B = B + A\overline{B} = A + B$$

10. (b)

### 11. (a)

·.·

·.·

A > B is

- 4221 code is a self complementing code.

- 4 + 2 + 2 + 1 = 9

- For a self complementing code system, codeword of "5" = 1's complement of codeword of "4"

- 5 = 9 4 i.e, 9's complement of 4.

- so, codeword of 5 = 1's complement of (1000)

#### 12. (d)

|                                          | A                     | 4       | E                     | }            |       |

|------------------------------------------|-----------------------|---------|-----------------------|--------------|-------|

|                                          |                       | ↓       |                       | $\Downarrow$ |       |

|                                          | <i>A</i> <sub>1</sub> | $A_0$   | <i>B</i> <sub>1</sub> | $B_0$        |       |

| possible when either of t                | he foll               | owing c | onditions             | is satis     | sfied |

| $A \setminus B \rightarrow i A$ when $G$ | - 1                   |         |                       |              |       |

- 1. When  $A_1 > B_1 \Rightarrow \text{i.e.}$ , when  $G_1 = 1$

- 2. When  $(A_1 = B_1)$  and  $(A_0 > B_0) \Rightarrow i.e.$ , when  $E_1G_0 = 1$

- So, the Boolean expression for G is

$G = E_1 G_0 + G_1$

#### 13. (a)

| Χ | Y | Ζ | Α |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| ∖ YZ | , I <sub>0</sub> | $I_1$ | $I_2$ | $I_3$ |

|------|------------------|-------|-------|-------|

| x    | 00               | 01    | 10    | 11    |

| 0    | 0                | 1     | 0     | 1     |

| 1    | 0                | 1     | 1     | 0     |

|      | 0                | 1     | x     | x     |

Thus solution is option (a).

#### 14. (b)

$T_{\rm min}$  = minimum clock period required

= time delay from the time of active clock edge to the point of time, where the latest change appears at the input of flip-flops before the application of next active clock edge.

Let us assume active clock edge is applied at t = 0, then

then,

the latest change in  $Q_0$  appears at  $\Rightarrow t = 5 \ \mu s$ the latest change in  $Q_1$  appears at  $\Rightarrow t = 4 \ \mu s$ the latest change in  $Q_2$  appears at  $\Rightarrow t = 3 \ \mu s$ the latest change in  $D_2$  appears at  $\Rightarrow t = 4 \ \mu s$ the latest change in  $D_1$  appears at  $\Rightarrow t = 4 \ \mu s$

```

the latest change in D_0 appears at \Rightarrow t = 10 \,\mu s

so T_{min} = 10 \,\mu sec

```

$$f_{c \max} = \frac{1}{T_{\min}} = \frac{1}{10 \,\mu \text{sec}} = 100 \,\text{kHz}$$

15. (a)

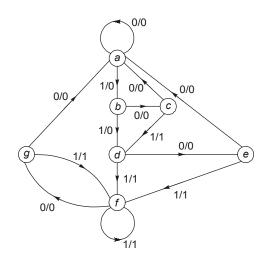

the state table for given state diagram:

| Present | Next        |             | Out         |             |

|---------|-------------|-------------|-------------|-------------|

| state   | for $X = 0$ | for $X = 1$ | for $X = 0$ | for $X = 1$ |

| а       | а           | b           | 0           | 0           |

| b       | с           | d           | 0           | 0           |

| с       | а           | d           | 0           | 1           |

| d       | е           | f           | 0           | 1           |

| е       | а           | f           | 0           | 1           |

| f       | g           | f           | 0           | 1           |

| g       | а           | f           | 0           | 1           |

state-g and state-e are equal, so we can replace state-g with state-e so, simplified state table will be,

| Present | Next        | state       | Output      |             |  |

|---------|-------------|-------------|-------------|-------------|--|

| state   | for $X = 0$ | for $X = 1$ | for $X = 0$ | for $X = 1$ |  |

| а       | а           | b           | 0           | 0           |  |

| b       | с           | d           | 0           | 0           |  |

| с       | а           | d           | 0           | 1           |  |

| d       | е           | f           | 0           | 1           |  |

| е       | а           | f           | 0           | 1           |  |

| f       | е           | f           | 0           | 1           |  |

now, state-f and state-d are equal. So, we can replace state-f with state-d so, simplified state table will be,

| Present | Next        | state       | Output      |             |  |

|---------|-------------|-------------|-------------|-------------|--|

| state   | for $X = 0$ | for $X = 1$ | for $X = 0$ | for $X = 1$ |  |

| а       | а           | b           | 0           | 0           |  |

| b       | с           | d           | 0           | 0           |  |

| С       | а           | d           | 0           | 1           |  |

| d       | е           | d           | 0           | 1           |  |

| е       | а           | d           | 0           | 1           |  |

now, state-*e* and state-*c* are equal. So, we can replace state-*e* with state-*c* so, simplified state table will be,

| Present | Next        | state       | Output      |             |  |

|---------|-------------|-------------|-------------|-------------|--|

| state   | for $X = 0$ | for $X = 1$ | for $X = 0$ | for $X = 1$ |  |

| а       | а           | b           | 0           | 0           |  |

| b       | с           | d           | 0           | 0           |  |

| с       | а           | d           | 0           | 1           |  |

| d       | с           | d           | 0           | 1           |  |

• it is not possible to reduce the state table further, as there are no more equal states.

• so, minimum number of states required to design the circuit = 4. and minimum number of flip-flops required = 2.

16. (b)

| Α | В | f     |

|---|---|-------|

| 0 | 0 | $P_1$ |

| 0 | 1 | $P_2$ |

| 1 | 0 | $P_3$ |

| 1 | 1 | $P_4$ |

so, the given pass logic network acts as EX-OR gate when  $P_1 = P_4 = 0$  and  $P_2 = P_3 = 1$ .

#### 17. (c)

The output z is connected from inverted outputs of the FFs through AND gate, i.e.

$$z = \bar{Q}_A \bar{Q}_B \bar{Q}_C = \overline{Q_A + Q_B + Q_C}$$

Hence, the output z will be high only when all FF's output are zero, i.e.  $Q_A = Q_B = Q_C = 0$ Let initially z = 1, then we obtain the truth table for the circuit as

|               | Pre            | esent          | State          |       |                | Inputs         | 5              |                |                | Nex     | kt Sta  | te      |   |

|---------------|----------------|----------------|----------------|-------|----------------|----------------|----------------|----------------|----------------|---------|---------|---------|---|

| CLK<br>number | Q <sub>A</sub> | Q <sub>B</sub> | Q <sub>c</sub> | $J_A$ | K <sub>A</sub> | J <sub>B</sub> | K <sub>B</sub> | J <sub>C</sub> | ĸ <sub>c</sub> | $Q_A^+$ | $Q_B^+$ | $Q_C^+$ | z |

| initial       | 0              | 0              | 0              | -     | -              | -              | -              | -              | -              | -       | -       | -       | 1 |

| 1             | 0              | 0              | 0              | 1     | 1              | 1              | 1              | 0              | 1              | 1       | 1       | 0       | 0 |

| 2             | 1              | 1              | 0              | 1     | 1              | 1              | 1              | 1              | 1              | 0       | 0       | 1       | 0 |

| 3             | 0              | 0              | 1              | 1     | 1              | 0              | 1              | 0              | 1              | 1       | 0       | 0       | 0 |

| 4             | 1              | 0              | 0              | 1     | 1              | 1              | 1              | 0              | 1              | 0       | 1       | 0       | 0 |

| 5             | 0              | 1              | 0              | 1     | 1              | 1              | 1              | 1              | 1              | 1       | 0       | 1       | 0 |

| 6             | 1              | 0              | 1              | 1     | 1              | 0              | 1              | 0              | 1              | 0       | 0       | 0       | 1 |

It is MOD-6 counter. So, output z will be 1 after 6 clock pulses.

#### 18. (b)

When  $Q_4 Q_3$  is 11, then CLR = 0, hence the count goes back to 00000.

Thus, counter counts 0 - 23, and clears at 24. It's a MOD-24 counter.

#### 19. (c)

$$f_{\max} = \frac{1}{nt_{pd}}$$

$t_{\rm pd}$  = propagation delay of each flip-flop and n = number of flip flops

$$t_{pd} = \frac{1}{n \times 25 \times 10^6} \sec$$

=  $\frac{1000}{4 \times 25} \times 10^{-9} \sec = 10 \operatorname{nsec}$

#### 20. (d)

| Clk No. | $Q_1$ | $Q_2$ |          |

|---------|-------|-------|----------|

| 0       | 0     | 0     | →initial |

| 1       | 1     | 0     |          |

| 2       | 1     | 1     |          |

| 3       | 0     | 1     |          |

| 4       | 0     | 0     |          |

It's a Johnson counter after 4 clock pulses the state  $(Q_1Q_0)$  will be (00) again.

#### 21. (b)

$$V_{0} = -R V_{\text{ref}} \left[ \frac{b_{3}}{2R} + \frac{b_{2}}{4R} + \frac{b_{1}}{8R} + \frac{b_{0}}{16R} \right]$$

=  $-\frac{V_{\text{ref}}}{16} \left[ 8b_{3} + 4b_{2} + 2b_{1} + b_{0} \right]$

$V_{0} = -\frac{V_{\text{ref}}}{16} \left[ \text{decimal equivalent of input binary code} \right]$

given input binary code =  $(0110)_{2} = (6)_{10}$

$V_{0} = \frac{10}{16}(6) = 3.75 \text{ V}$

22. (c)

SO,

#### 23. (c)

Output of the 4 : 1 MUX circuit in Figure A is

$$Y = I_0 \overline{A} \overline{B} + I_1 \overline{A} B + I_2 A \overline{B} + I_3 A B$$

Output of the circuit in Figure B is

$Y = A \oplus B \oplus C = \overline{A}\overline{B}C + \overline{A}B\overline{C} + A\overline{B}\overline{C} + ABC$

On comparison

$$I_0 = C$$

$$I_1 = \overline{C}$$

$$I_2 = \overline{C}$$

$$I_3 = C$$

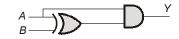

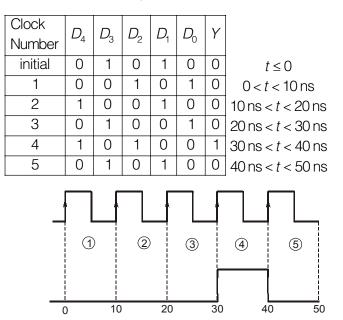

24. (c)

$Y = (A \oplus B) \cdot A = (\overline{A}B + A\overline{B}) \cdot A$

$= A\overline{B} = D_2 \cdot \overline{D}_0$

The LED will be in ON state for 30 ns < t < 40 ns. So, option (c) is the correct answer.

#### 25. (b)

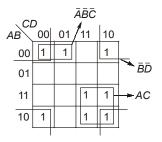

The k-map has to rearranged as

26. (c)

$$F = \overline{A}\overline{B}\overline{C} + \overline{B}\overline{D} + AC$$

$$F = \overline{(A+B)C+D}$$

### 27. (a)

In the circuit, we have

$$D_0 = \overline{Q_1 Q_2} = \overline{Q}_1 + \overline{Q}_2$$

$$D_1 = Q_0$$

$$D_2 = Q_1$$

The truth table for the circuit is obtained below.

|               | Present State         |                |                |                | Inputs                |                       |         | Next State |         |  |

|---------------|-----------------------|----------------|----------------|----------------|-----------------------|-----------------------|---------|------------|---------|--|

| CLK<br>number | <b>Q</b> <sub>2</sub> | Q <sub>1</sub> | Q <sub>0</sub> | D <sub>2</sub> | <i>D</i> <sub>1</sub> | <i>D</i> <sub>0</sub> | $Q_2^+$ | $Q_1^+$    | $Q_0^+$ |  |

| initial       | 0                     | 0              | 0              | -              | -                     | -                     | -       | -          | -       |  |

| 1             | 0                     | 0              | 0              | 0              | 0                     | 1                     | 0       | 0          | 1       |  |

| 2             | 0                     | 0              | 1              | 0              | 1                     | 1                     | 0       | 1          | 1       |  |

| 3             | 0                     | 1              | 1              | 1              | 1                     | 1                     | 1       | 1          | 1       |  |

| 4             | 1                     | 1              | 1              | 1              | 1                     | 0                     | 1       | 1          | 0       |  |

After 4 clock pulses, output is  $Q_2 Q_1 Q_0 = 110$

### 28. (c)

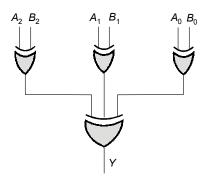

Redrawing the digital circuit

From the figure we get,

$$Y = A_0 \oplus B_0 \oplus A_1 \oplus B_1 \oplus A_2 \oplus B_2$$

So, Y is XOR of six boolean variables and Y will be 1 when odd number of variable are 1. Thus there will

be

$$\frac{2^6}{2} = 32$$

cases for the output to be 1.

| <b>Q</b> <sub>0</sub> | Q <sub>1</sub> | $J_0$ | K <sub>0</sub> | J <sub>1</sub> | <i>K</i> <sub>1</sub> | <b>Q</b> _0^+ | $Q_1^+$ |           |

|-----------------------|----------------|-------|----------------|----------------|-----------------------|---------------|---------|-----------|

| 0                     | 0              | 1     | 1              | 0              | 1                     | 1             | 0       | 5         |

| 1                     | 0              | 1     | 1              | 1              | 0                     | 0             | 1       | > MOD = 3 |

| 0                     | 1              | 0     | 1              | 0              | 1                     | 0             | 0       | )         |

| 0                     | 0              | 1     | 1              | 0              | 1                     | 1             | 0       |           |

| 1                     | 0              | 1     | 1              | 1              | 0                     | 0             | 1       |           |

| 0                     | 1              | 0     | 1              | 0              | 1                     | 0             | 0       |           |

#### 30. (b)

Since its an inverting amplifier,

MADE EASY

$V_{\rm out} = -9.375 \, {\rm V} \qquad {\rm when} \ |V_{\rm out}| = 9.375 \, {\rm V}$  maximum output means all bits are 1

$b_0 b_1 b_2 \dots b_n = 1111 \dots 1$ i.e.,

$$V_{\text{out}} = -V\left(\frac{R}{R}b_0 + \frac{R}{2R}b_1 + \frac{R}{4R}b_2 + \frac{R}{8R}b_3 \dots + \frac{R}{2^{n-1}R}b^n\right)$$

-9.375 =  $-5\left(1 + \frac{1}{2} + \frac{1}{4} + \frac{1}{8} + \dots + \frac{1}{2^{n-1}}\right)$

$1.875 = \frac{\left(1 - \left(\frac{1}{2}\right)^n\right)}{1 - \frac{1}{2}}$

$\frac{1}{2} \times 1.875 = 1 - \left(\frac{1}{2}\right)^n$

$\left(\frac{1}{2}\right)^n = 1 - \frac{1}{2} \times 1.875 = 0.0625 = \frac{1}{16}$

$2^n = 16$

$n = 4$

SO,