# B RANK IMPROVEMENT BATCH ELECTRICAL ENGINEERING

# RIB-W | T1

R

Session 2019 - 20 | S.No. : 220619\_LS1

| ANSWER KEY |     | > | Dig | jital E | lectronics |     |     |     |     |     |

|------------|-----|---|-----|---------|------------|-----|-----|-----|-----|-----|

| 1.         | (c) |   | 7.  | (a)     | 13.        | (c) | 19. | (b) | 25. | (a) |

| 2.         | (c) |   | 8.  | (d)     | 14.        | (c) | 20. | (c) | 26. | (b) |

| 3.         | (c) |   | 9.  | (c)     | 15.        | (d) | 21. | (d) | 27. | (d) |

| 4.         | (b) |   | 10. | (c)     | 16.        | (a) | 22. | (c) | 28. | (c) |

| 5.         | (b) |   | 11. | (c)     | 17.        | (a) | 23. | (b) | 29. | (a) |

| 6.         | (b) |   | 12. | (b)     | 18.        | (c) | 24. | (a) | 30. | (d) |

# **DETAILED EXPLANATIONS**

1. (c)

$(AB + B\overline{C} + \overline{A}C) (A + C) = AB + AB\overline{C} + ABC + \overline{A}C$  $= AB + \overline{A}C$

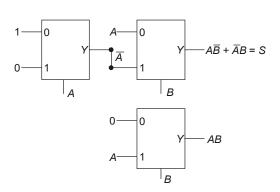

2. (c)

#### MADE EASY India's Best Institute for IES, GATE & PSUB

#### 3. (c)

number of flip-flops required = 4maximum delay =  $4 \times 10$  nsec = 40 nsec

#### 4. (b)

Total number of states possible with 11 flip-flops =  $2^{11} = 2048$ Required states = 2014 Number of states to be eliminated

= 2048 - 2014 = 34

#### 5. (b)

When MOD 5 and MOD 4 counters are cascaded, the combination becomes MOD 20 counter.

So, output frequency,  $f_0 = \frac{f_i}{20} = \frac{20}{20} = 1 \text{ MHz}$

#### 6. (b)

In 2's complement data representation, range with n-bit is:  $-(2^{n-1})$  to  $+(2^{n-1}-1)$ . So, 8-bit 2's complement can represent numbers between -128 to +127.

#### 7. (a)

In the given digital circuit each multiplexer is working as a NOT gate thus it is a ring oscillator with five

NOT gates. The frequency of oscillation will be  $f = \frac{1}{2Nt_{pd}}$ .

N = number of NOT gates in cascade

$t_{pd}$  = propagation delay of each NOT gate.

$$\therefore \qquad f = \frac{1}{2 \times 5 \times 25 ns} = 4 \times 10^6 \text{ Hz} = 4 \text{ MHz}.$$

#### 8. (d)

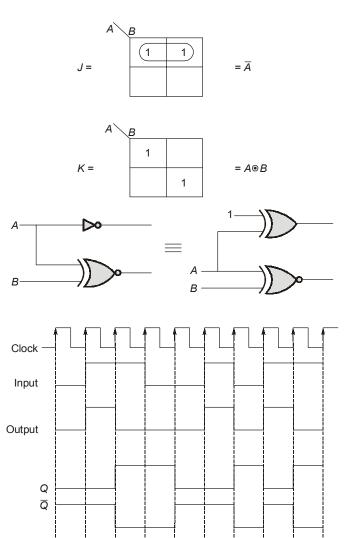

From the figure  $J = \overline{Q}, K = 1$ .

| Clock | J | K | Q  | $Q^{\dagger}$ |

|-------|---|---|----|---------------|

| -     | 1 | 1 | 0  | Ι             |

| 1     | 1 | 1 | 0  | _1            |

| 2     | 0 | 1 | 1* | 0             |

| 3     | 1 | 1 | 0  | 1             |

| 4     | 0 | 1 | 1  | 0             |

| 5     | 1 | 1 | 0  | 1             |

Hence, sequence of *Q* is 010101.

### 9. (c)

Divide by 78 counter can be realized by using cascade of MOD-13 and MOD-6 counter.

10. (c)

$$Q^{+} = \overline{X}\overline{Y} + X\overline{Y}Q + \overline{X}Y\overline{Q} = \overline{Y}[\overline{X} + XQ] + \overline{X}Y\overline{Q}$$

$$= \overline{Y}\overline{X} + \overline{Y}Q + \overline{X}Y\overline{Q} = \overline{Y}Q + \overline{X}[\overline{Y} + Y\overline{Q}] = \overline{Y}Q + \overline{X}\overline{Y} + \overline{X}\overline{Q}$$

$$Q^{+} = \overline{Y}Q + \overline{X}\overline{Q}$$

[using Consensus Law]

11. (c)

| 1 | 1 | 1 |   |

|---|---|---|---|

| G | А | Т | Е |

| + | Е | Е | Е |

| Т | 7 | Е | Α |

# 13. (c)

$$S_{1} = A \oplus B$$

$$C_{1} = AB$$

$$S = (A \oplus B) \oplus AB = (A \oplus B) \cdot \overline{AB} + (\overline{A \oplus B}) \cdot AB$$

$$= (A\overline{B} + \overline{AB}) (\overline{A} + \overline{B}) + (AB + \overline{AB}) (A, B) = A\overline{B} + \overline{AB}) + AB = A + B$$

$$C = (A \oplus B) \cdot AB = (A\overline{B} + \overline{AB}) \cdot AB = 0$$

14. (c)

| $Q_3$ | $Q_2$ | $Q_1$ |              |                             |   |   |   |  |

|-------|-------|-------|--------------|-----------------------------|---|---|---|--|

| 0     | 0     | 0     | $\leftarrow$ | Initial state               |   |   |   |  |

| 0     | 0     | 1     |              | 1 <sup>st</sup> clock pulse |   |   |   |  |

| 0     | 1     | 1     |              | 2 <sup>nd</sup> clock pulse |   |   |   |  |

| 1     | 0     | 1     |              | 3 <sup>rd</sup> clock pulse |   |   |   |  |

| 0     | 0     | 0     |              | 4 <sup>th</sup> clock pulse |   |   |   |  |

|       | e     |       |              |                             | ~ | ~ | ~ |  |

$\Rightarrow$  Modulus of the counter is 4, After 8 clock pulses  $Q_3 Q_2 Q_1$  will be 101

# 15. (d)

From the figure we can see that

- 1<sup>st</sup> change at 1 ns is accepted, so 6<sup>th</sup> bit i.e. *MSB* is 1

- $2^{nd}$  change at t = 2 ns is not accepted, so  $5^{th}$  bit is 0.

- $3^{rd}$  change at t = 3 ns is not accepted, so  $4^{th}$  bit is 0.

- $4^{\text{th}}$  change at t = 4 ns is accepted, so  $3^{\text{rd}}$  bit is 1.

- $5^{\text{th}}$  change at t = 5 ns is not accepted, so  $2^{nd}$  bit is 0.

- $6^{\text{th}}$  change at t = 6 ns is accepted, so  $1^{\text{st}}$  bit is 1.

So, digital output is  $(100101)_2$ .

# 16. (a)

The following table represent the output of the multiplexer.

| Clock | Cou            | utput          | MUX Input      |                |       | Output |                |

|-------|----------------|----------------|----------------|----------------|-------|--------|----------------|

| CIOCK | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | S <sub>1</sub> | $S_0$ | Enable | Output         |

| _     | 1              | 0              | 1              | 0              | 1     | 1      | I <sub>1</sub> |

| 1     | 1              | 0              | 0              | 0              | 1     | 0      | 0              |

| 2     | 0              | 1              | 1              | 1              | 0     | 1      | $I_2$          |

| 3     | 0              | 1              | 0              | 1              | 0     | 0      | 0              |

# 17. (a)

Since, % accuracy is 0.02 thus the maximum error will be

= maximum output

$$\times \frac{(0.02)}{100} = 5 \times \frac{(0.02)}{100} = 1 \text{ mV}$$

www.madeeasy.in

## 18. (c)

The input D is  $Q_0 \oplus Q_2 \oplus Q_3$ .

| Clock | D | Q <sub>3</sub> | Q <sub>2</sub> | <b>Q</b> <sub>1</sub> | <b>Q</b> <sub>0</sub> |

|-------|---|----------------|----------------|-----------------------|-----------------------|

| _     | _ | 1              | 0              | 0                     | 0                     |

| 1     | 1 | 1              | 1              | 0                     | 0                     |

| 2     | 0 | 0              | 1              | 1.                    | 0                     |

| 3     | 1 | 1              | 0              | 1                     | 1                     |

| 4     | 0 | 0              | 1              | 0                     | 1                     |

| 5     | 0 | 0              | 0              | 1                     | 0                     |

| 6     | 0 | 0              | 0              | 0                     | 1                     |

Hence, the pattern 0001 appears at 6<sup>th</sup> pulse.

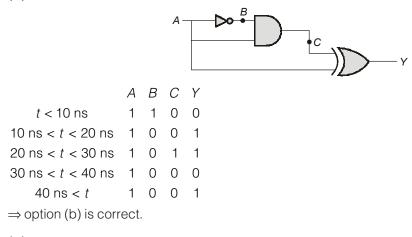

19. (b)

$$Y = \overline{ABC + \overline{A}\overline{B}} + BC$$

Dual of Y

$$Y_{d} = \overline{(A+B+C) \cdot (\overline{A}+\overline{B})} \cdot (B+C)$$

$$= \left[\overline{(A+B+C)} + \overline{(\overline{A}+\overline{B})}\right] \cdot (B+C)$$

Compliment of Y

$$Y_{c} = \overline{(\overline{ABC} + \overline{\overline{AB}}) + BC} = (\overline{\overline{ABC} + \overline{\overline{AB}}}) \cdot \overline{BC} = (ABC + \overline{\overline{AB}}) \cdot \overline{BC}$$

### 21. (d)

State Table

| A | В | $Q_{n+1}$        | J | Κ |

|---|---|------------------|---|---|

| 0 | 0 | $\overline{Q}_n$ | 1 | 1 |

| 0 | 1 | 1                | 1 | 0 |

| 1 | 0 | $Q_n$            | 0 | 0 |

| 1 | 1 | 0                | 0 | 1 |

By checking all the options option (c) correctly matches.

# 23. (b)

$\begin{array}{lllllllllll} & Q_0 &= & Q_1 = 0 \\ \Rightarrow & Y_0 &= & 0 \\ \Rightarrow & J - & K \mbox{ flip-flop is cleared} \\ Q_A &= & 0 & \bar{Q}_A &= & 1 \\ As \mbox{ clock pulse is applied counter starts up counting} \\ As \mbox{ counter reaches } & Q_1 &= & 1, \ Q_0 &= & 1 \mbox{ after 3 clock pulses } J - & K \mbox{ flip flop is preset.} \\ \Rightarrow & Q_A &= & 1 & \bar{Q}_A &= & 0 \end{array}$

$\Rightarrow$  Counter starts down counting until  $Y_0$  is low and this repeats.

So, Output  $Q_1 Q_0$  in decimal form is

0, 1, 2, 3, 2, 1, 0, 1....

#### 24. (a)

$$\overline{\text{Chip select}} = \overline{(A_2 \odot A_3) \cdot [(A_4 \odot A_5) + (A_6 \odot A_7)]}$$

Chip select =  $(A_2 \odot A_3) \cdot [(A_4 \odot A_5) + (A_6 \odot A_7)]$

Chip select will be '1' when

$[(A_2 = A_3) \text{ and } (A_4 \neq A_5) \text{ and } (A_6 \neq A_7)]$

Since  $A_1$ ,  $A_0$  are not present in expression of chip select they can have any value. So the address combination for chip select = 1 are

|   | A <sub>7</sub> | $A_6$ | $A_5$ | $A_4$ | $A_3$ | $A_2$ | <i>A</i> <sub>1</sub> | $A_0$ |

|---|----------------|-------|-------|-------|-------|-------|-----------------------|-------|

| 1 | 0              | 1     | 1     | 0     | 0     | 0     | ×                     | ×     |

| 2 | 1              | 0     | 1     | 0     | 0     | 0     | ×                     | ×     |

| 3 | 1              | 0     | 0     | 1     | 0     | 0     | ×                     | ×     |

| 4 | 0              | 1     | 0     | 1     | 0     | 0     | ×                     | ×     |

| 5 | 0              | 1     | 1     | 0     | 1     | 1     | ×                     | ×     |

| 6 | 1              | 0     | 1     | 0     | 1     | 1     | ×                     | ×     |

| 7 | 1              | 0     | 0     | 1     | 1     | 1     | ×                     | ×     |

| 8 | 0              | 1     | 0     | 0     | 1     | 1     | ×                     | ×     |

We get 8 combinations only 1st combination match with option a

# 25. (a)

In the circuit, we have

$$D_0 = \overline{Q_1 \cdot Q_2} = \overline{Q}_1 + \overline{Q}_2$$

$$D_1 = Q_0$$

$$D_2 = Q_1$$

The truth table for the circuit is obtained below.

|     |                | Input |       | Output         |                       |       |

|-----|----------------|-------|-------|----------------|-----------------------|-------|

| CLK | D <sub>2</sub> | $D_1$ | $D_0$ | Q <sub>2</sub> | <b>Q</b> <sub>1</sub> | $Q_0$ |

| 0   | 0              | 0     | 1     | 0              | 0                     | 0     |

| 1   | 0              | 1     | 1     | 0              | 0                     | 1     |

| 2   | 1              | 1     | 1     | 0              | 1                     | 1     |

| 3   | 1              | 1     | 0     | 1              | 1                     | 1     |

| 4   | 1              | 0     | 0     | 1              | 1                     | 0     |

| 5   | 0              | 0     | 0     | 1              | 0                     | 0     |

The D-flip flop transfer the data from input to output, if CLK pulse is given. After 4 clock pulses, output is  $Q_2 Q_1 Q_0 = 110$

# 26. (b)

Since clock is applied to  $\div$  12 counter. The AND gates have open collector output so RST will be '1' if both the AND gates produce '1'. Thus RST will be 1 when output of top counter is '0110' and output of bottom counter is '1001'. From the circuit we can determine that after every twelve pulses of clock, one pulse of CLK reach to the top counter. So,

| Clock    | Output of bottom counter | Output of top counter | Ζ      |

|----------|--------------------------|-----------------------|--------|

| 0        | 0000                     | 0000                  | 0      |

| 11<br>12 | 1011<br>0000             | 0000<br>0001          | 0<br>0 |

| 23<br>24 | 1011<br>0000             | 0001<br>0010          | 0<br>0 |

| 35<br>36 | 1011<br>0000             | 0010<br>0011          | 0<br>0 |

| 47<br>48 | 1011<br>0000             | 1011<br>0100          | 0<br>1 |

| 59<br>60 | 1011<br>0000             | 0100<br>0101          | 1<br>1 |

| 71<br>72 | 1011<br>0000             | 0101<br>0110          | 1<br>1 |

| 81<br>82 | 1001<br>0000             | 0110<br>0000          | 0<br>0 |

So Z remain 1 for (12 + 12 + 9) clock cycles

So duty cycle =

$$\frac{12+12+8}{12+12+12+12+12+12+8} \times 100 = 39.5\%$$

27. (d)

$$S_{1} = SUM = A \oplus B \text{ and } S_{0} = CARRY = A. B$$

$$Y = S'_{1}S'_{0}I_{0} + S'_{1}S_{0}I_{1} + S_{1}S'_{0}I_{2} + S_{1}S_{0}I_{3}$$

$$= (A \oplus B)'(AB)'C + (A \oplus B)'(AB)C + (A \oplus B)(AB)'C' + (A \oplus B)(AB)C'$$

$$Y = A \oplus B \oplus C$$

#### 28. (c)

Given circuit is of 8 to 1 multiplexer. Multiplexer is used to select any one input out of all inputs at a time. Hence, output will be equal to  $I_5$  for a particular combination of selection lines.

For D = 1; C = 0; A = 1combination selects the  $I_5$ . Also, we have the given logic function as F = AC + ABD + ACD + BCDSo, by substituting D = 1, C = 0, and A = 1,We get F = 0 + B + 0 + 0 F = B

Thus, input to  $I_5$  must be equal to B.

# 29. (a)

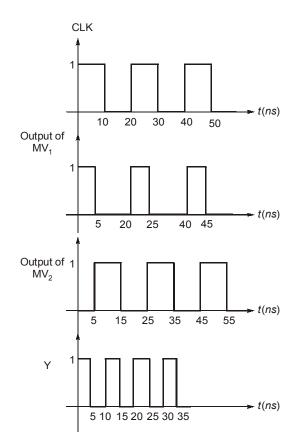

Since  $Y = (\text{output of } MV_2) \oplus CLK$ So the time period of Y is 100 MHz

# 30. (d)

A = 10 10 10 10 B = 11 11 11 11 Ex-NOR : 10 10 10 10

Gray code of 10 10 10 10 is 11 11 11 11 Decimal equivalent of (11111111) = 255

####