# **ESE 2025 : Mains Test Series**

ENGINEERING SERVICES EXAMINATION

## **Electronics & Telecommunication Engineering**

Test-2: Digital Circuits + Signals and Systems + Microprocessors & Microcontroller [All topics]

| Name :       |             |          | *************************************** |                     |

|--------------|-------------|----------|-----------------------------------------|---------------------|

| Roll No :    |             |          |                                         |                     |

| Test Centres |             |          |                                         | Student's Signature |

| Delhi 🗆      | Bhopal 🖂    | Jaipur 🗌 | Pune 🗌                                  |                     |

| Kolkata 🗌    | Hyderabad 🗌 |          |                                         |                     |

#### Instructions for Candidates

- 1. Do furnish the appropriate details in the answer sheet (viz. Name & Roll No).

- 2. There are Eight questions divided in TWO sections.

- 3. Candidate has to attempt FIVE questions in all in English only.

- 4. Question no. 1 and 5 are compulsory and out of the remaining THREE are to be attempted choosing at least ONE question from each section.

- 5. Use only black/blue pen.

- 6. The space limit for every part of the question is specified in this Question Cum Answer Booklet. Candidate should write the answer in the space provided.

- 7. Any page or portion of the page left blank in the Question Cum Answer Booklet must be clearly struck off.

- 8. There are few rough work sheets at the end of this booklet. Strike off these pages after completion of the examination.

| FOR OFF                 | ICE USE        |  |

|-------------------------|----------------|--|

| Question No.            | Marks Obtained |  |

| Section                 | on-A           |  |

| Q.1                     | 36             |  |

| Q.2                     | 39             |  |

| Q.3                     | 1              |  |

| Q.4                     |                |  |

| Section                 | on-B           |  |

| Q.5                     | 41             |  |

| Q.6                     | 44             |  |

| Q.7                     | 30             |  |

| Q.8                     | 1              |  |

| Total Marks<br>Obtained | 190            |  |

Signature of Evaluato

Cross Checked by

### IMPORTANT INSTRUCTIONS

CANDIDATES SHOULD READ THE UNDERMENTIONED INSTRUCTIONS CAREFULLY. VIOLATION OF ANY OF THE INSTRUCTIONS MAY LEAD TO PENALTY.

### **DONT'S**

- Do not write your name or registration number anywhere inside this Question-cum-Answer Booklet (QCAB).

- 2. Do not write anything other than the actual answers to the questions anywhere inside your QCAB.

- 3. Do not tear off any leaves from your QCAB, if you find any page missing do not fail to notify the supervisor/invigilator.

- 4. Do not leave behind your QCAB on your table unattended, it should be handed over to the invigilator after conclusion of the exam.

#### DO'S

- 1. Read the Instructions on the cover page and strictly follow them.

- Write your registration number and other particulars, in the space provided on the cover of QCAB.

- 3. Write legibly and neatly.

- For rough notes or calculation, the last two blank pages of this booklet should be used. The rough notes should be crossed through afterwards.

- 5. If you wish to cancel any work, draw your pen through it or write "Cancelled" across it, otherwise it may be evaluated.

- 6. Handover your QCAB personally to the invigilator before leaving the examination hall.

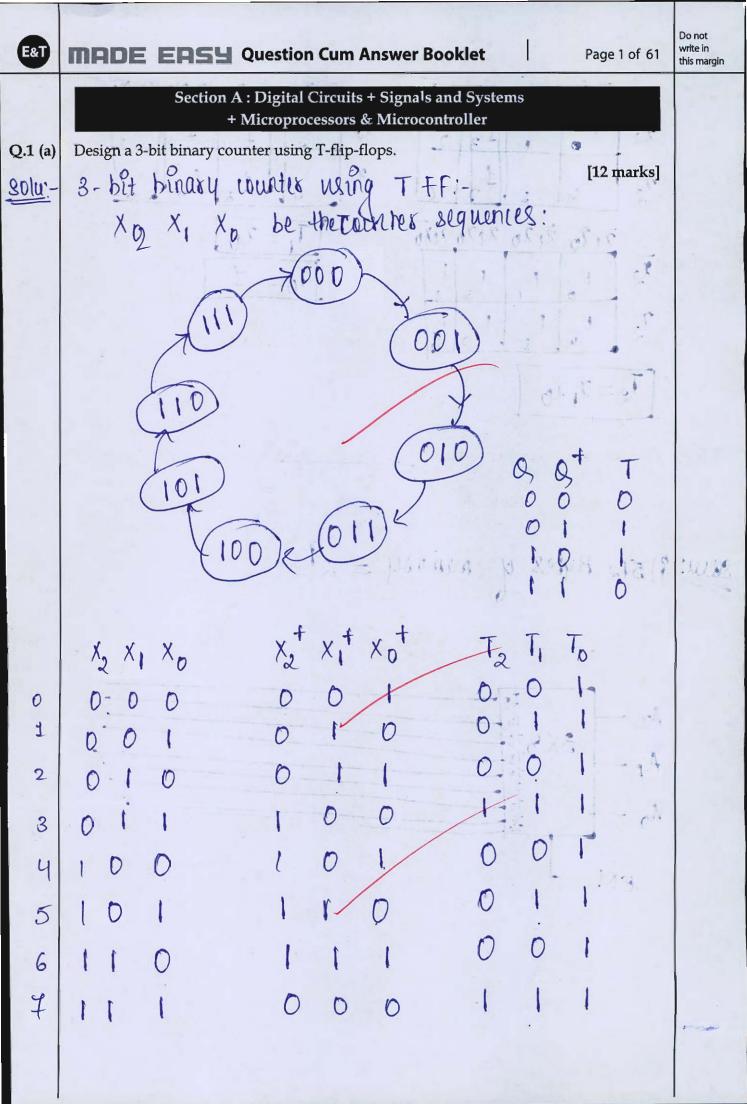

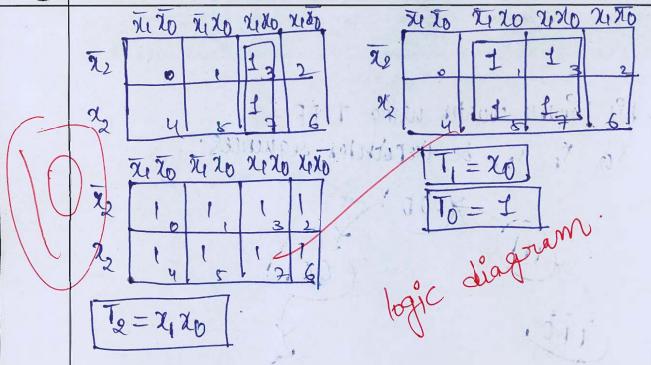

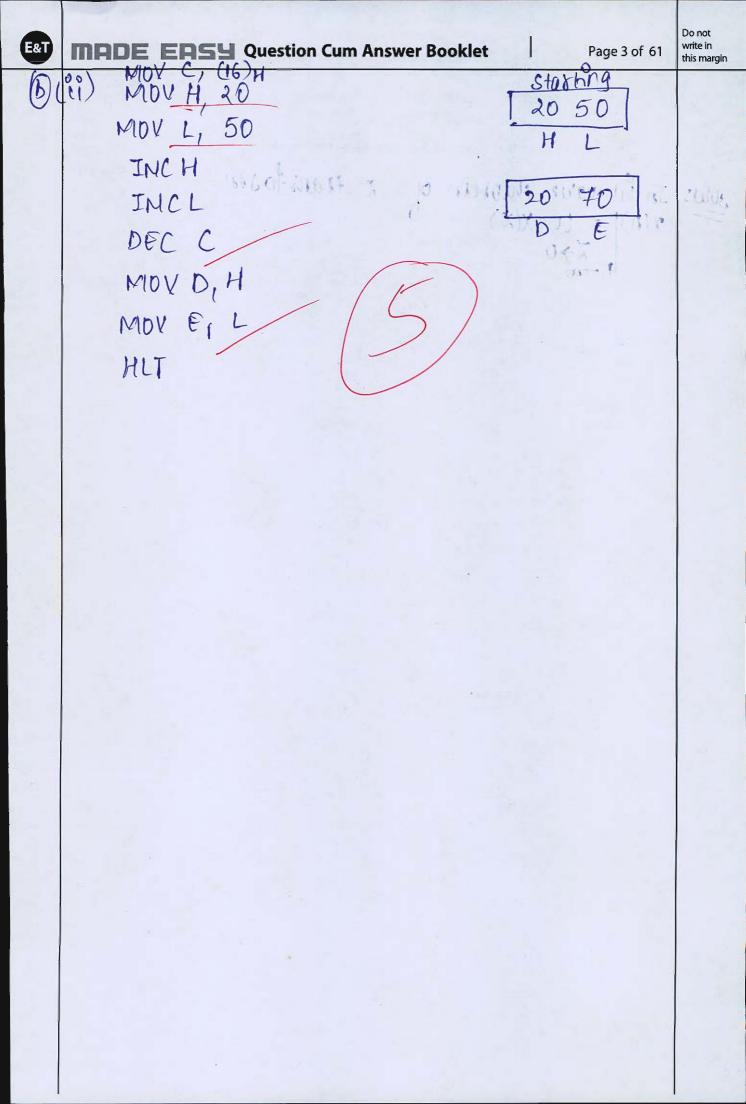

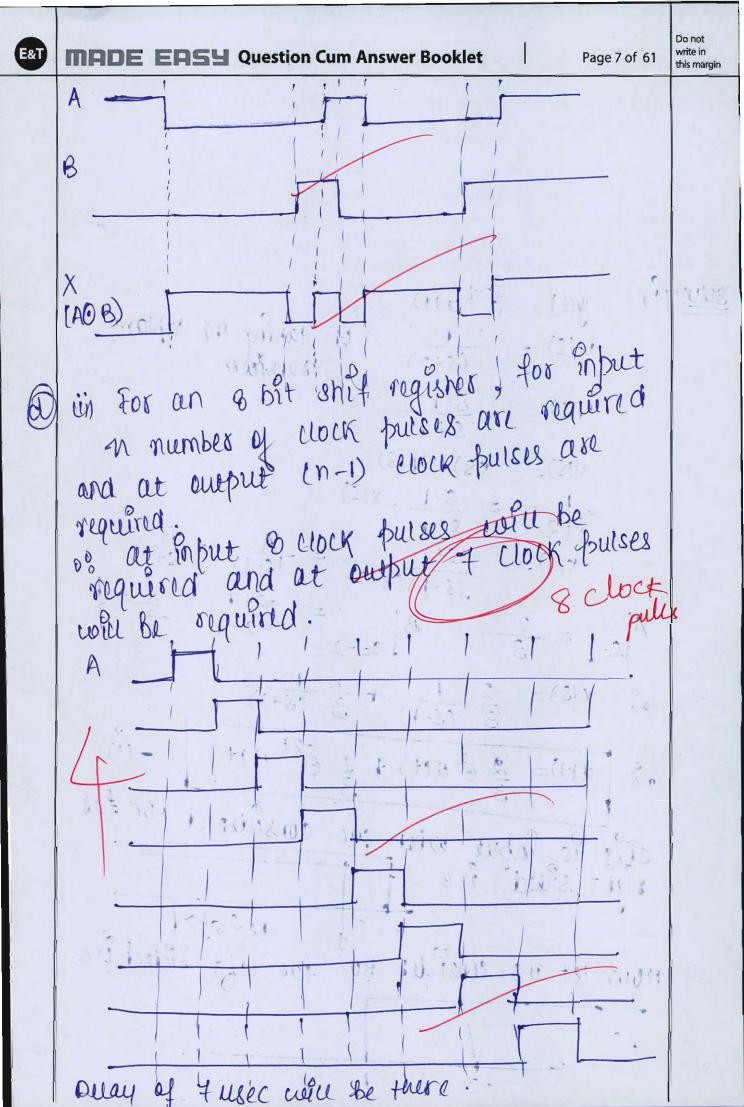

- Q.1 (b)

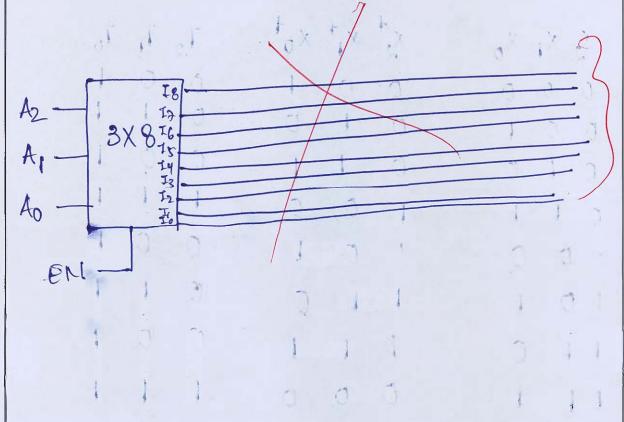

- (i) Draw the circuit for interfacing 512 bytes of memory to 8085 microprocessor using 3 × 8 decoder.

- (ii) Write an assembly language program to move a block of Data of 16 bytes starting from address 2050H to another location starting from 2070H in 8085 microprocessor.

sou: 9) 512 Bytes of memory = 29

[7 + 5 marks]

- Q.1 (c)

- (i) Draw the signal flow graph (Butterfly structure) for the computation of 8-point IDFT using inverse Radix-2 DIF-FFT.

- (ii) State and prove Initial-value theorem of z-transform.

3011

Intial value thiorem of z transform x(n) = Lt x(z)

[8 + 4 marks]

- Q.1 (d)

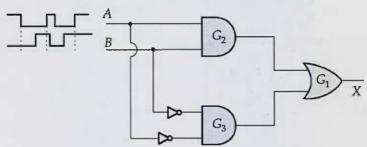

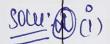

- (i) Draw the timing diagram for the logic circuit in the figure shown with outputs of  $G_1$ ,  $G_2$  and  $G_3$  with input waveform A and B as indicated.

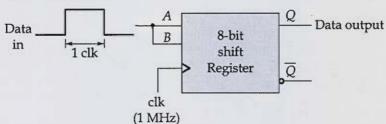

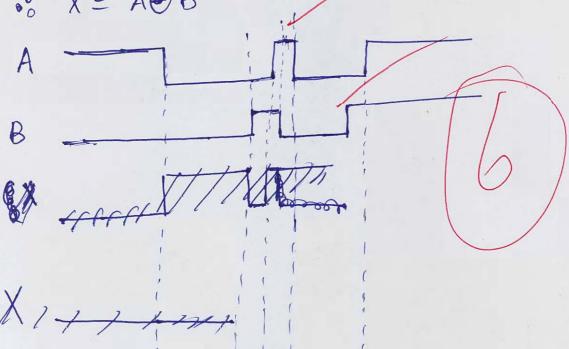

(ii) Consider the serial in-serial out shift register which is used to provide time delay from input to output.

Draw and calculate the output and delay provided by the above shift register in clear steps.

[6 + 6 marks]

clear steps.

$$G_{2} = A \cdot B$$

$$G_{3} = A \cdot B$$

$$G_{4} = A \cdot B$$

$$G_{5} = A \cdot B + A \cdot B = A \cdot B = A$$

$$G_{6} = G_{3} + G_{2} = A \cdot B + A \cdot B = A \cdot B = A$$

Q.1 (e)

Consider the signal  $y(t) = e^{-2t}u(t)$  is the output of a causal all-pass system for which the system function is

$$H(s) = \frac{s-1}{s+1}$$

- (i) Find and sketch at least two possible inputs x(t) that could produce y(t).

- (ii) From the solutions obtained in part (i), what is the input x(t) if it known that a stable system exists that will have x(t) as an output and y(t) as the input? Find the impulse response h(t) for this system.

<u>solu:</u> (1)

$y(t) = e^{2t}u(t)$  on taking the laplace  $y(t) = \frac{1}{(s+2)}$  transform.

$M(S) = \frac{S-1}{S+1}$

415) = X/S) . H(S)

S+2 S+1 . XIS

(S-1)(S+2)

$A|_{S=1} = \frac{2}{3}$   $B|_{S=-2} = \frac{-2+1}{-2-1} = \frac{-3}{3} = \frac{3}{3}$

$000 \times (S) = \frac{2}{3} \frac{1}{(S-1)} + \frac{1}{3} \frac{1}{(S+2)}$

$\frac{3}{3}(3-1)$  =  $\frac{2}{3}e^{t}u(t) + \frac{1}{3}e^{2t}u(t) - (1)$

shis is input when we considered ROC for right sided i.e.

Mous let us consider Roc for left sided ise

ellan of H

$$\frac{1}{2} \times (S) = \frac{2}{3} \frac{1}{(S+1)} + \frac{1}{3} \frac{1}{(S+2)}$$

:.

$$(x) = \frac{-2}{3}e^{t}(t+t) + \frac{1}{3}(t+t)e^{t}(t+t) - (1)$$

(i) 4 (ĉi) represents two possible input xet)

that acurd produce yet).

Etij since we know for system to be stable it should have go axis is considered in equation (i) 4 (ii) joo axis is considered

use can choose any one solution.

tet  $y(s) = \frac{s+1}{(s-1)(s+2)}$

$$4 \times (S) = \frac{1}{(S+2)}$$

$$\frac{(S+1)(S+2)}{(S-1)(S+2)} = H(S)$$

$$H(S) = \begin{bmatrix} S+1 \\ S-1 \end{bmatrix}$$

$$H(S) = \frac{S}{S-1} + \frac{1}{S-1} = \frac{Q}{S-1} + \frac{1}{S-1}$$

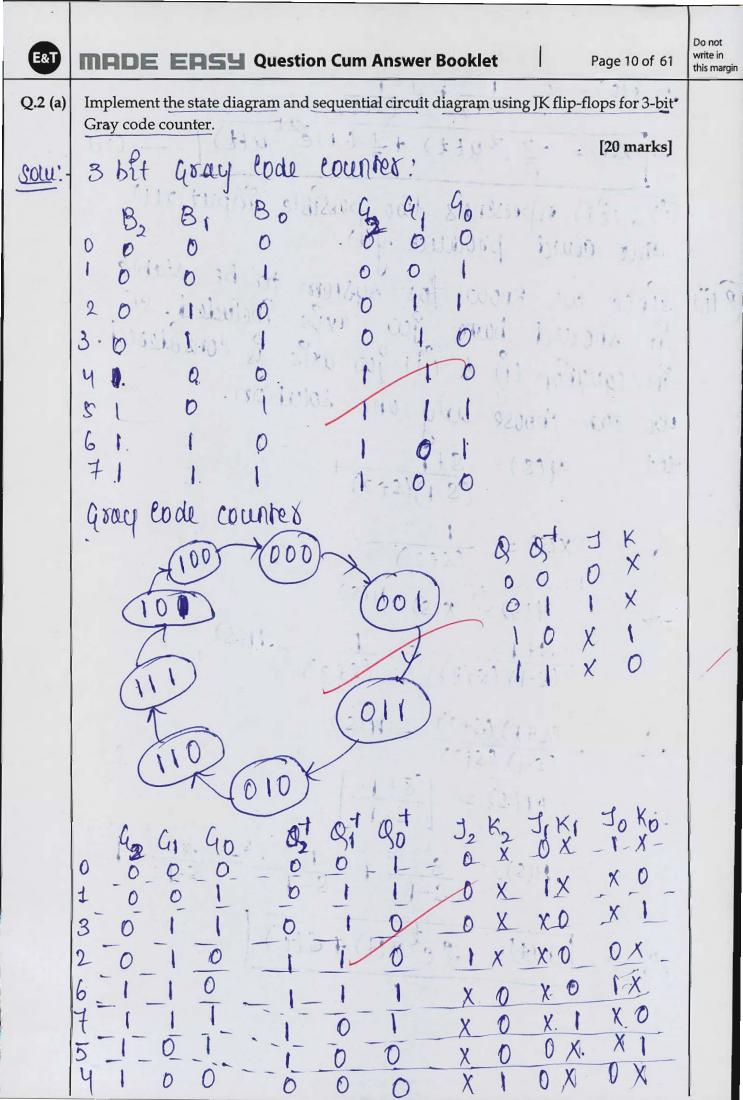

- Q.2(b)

- Determine and sketch y(t), the convolution of the two signals given below: (i)

$$x(t) = \begin{cases} 2, & -1 \le t \le 1 \\ 1, & 1 < t \le 3 \\ 0, & \text{elsewhere} \end{cases}$$

and  $h(t) = 2\delta(t+1) + \delta(t+2)$

The output y(t) of a causal LTI system is related to the input x(t) by the equation

$$\frac{dy(t)}{dt} + 10y(t) = \int_{0}^{\infty} x(\tau)z(t-\tau)d\tau - x(t)$$

where.

$$z(t) = e^{-t}u(t) + \delta(t)$$

Determine the impulse response of the system.

sow.

$$(1) \text{ 2H} \leftrightarrow 2 \Rightarrow \text{3uH+D-uH-1}-\text{uH-1}$$

$$y(t) = aut) * h(t)$$

$y(t) = [au(t+1) - v(t-1) - v(t-3)] * [as(t+1) + s(t+2)]$

(11)

$$\frac{dyt}{dt} + loy(t) = \int_{-\infty}^{\infty} \chi(t) \chi(t-t) dt - \chi(t)$$

$$u(s) = x(s) [x(s) -1]$$

$$\frac{1 - (2)x}{(2)x} = \frac{(2)y}{(2)x}$$

I en taking cap (alle that spotter), as

$$t = \frac{1}{(S+1)} = \frac{S+2}{S+1}$$

$$\frac{y(s)}{x(s)} = H(s) = \frac{842 - 1}{841} = \frac{(s+2) - (s+1)}{(s+1)(s+10)}$$

$$1(S) = \frac{1}{(S+1)(S+10)} = \frac{A}{(S+1)} + \frac{B}{(S+10)}$$

$$A|_{S=-1} = \frac{1}{9}$$

$B|_{S=-10} = \frac{1}{10+1} = \frac{1}{9}$

$$H(S) = \frac{1}{9} \frac{1}{(S+1)} - \frac{1}{9} \frac{1}{(S+10)}$$

$$h(t) = \frac{1}{9} e^{t} u(t) - \frac{1}{9} e^{10t} u(t)$$

Do not write in

this margin

Q.2 (c)

(i) Interface 4 KB memory to 8085 with starting address A000H.

Design address decoding circuit using (i) 3 × 8 decoder and (ii) using only NAND gates.

(+13,4/41)

(ii) Write an algorithm and assembly language program, to perform the multiplication of two 8 bit numbers using 8085.

golu

(i)  $UKB = 2^2 \times 2^{10} = 2^{12}$  [10 + 10 marks] of there will be 12 address lines

starting Address + Ending Address-1=Ffff

Ending address = ffff-A000H+1

= 6000H

Q.3 (a)

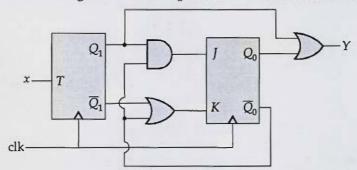

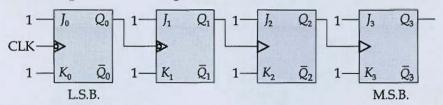

(i) Draw the state diagram of the sequential circuit shown in figure below:

(ii) Find the z-transform of the given signal x[n] using scaling in the z-domain property.

$$x[n] = a^n \sin(\omega_0 n) u[n].$$

[10 + 10 marks]

## MADE EASY Question Cum Answer Booklet

Page 20 of 61

Do not write in this margin

- Q.3 (b)

- (i) Implement the following Boolean function using 3 × 4 × 2 PLA, also write the PLA programming table.

$$F_1(A, B, C) = \Sigma m(0, 1, 2, 4)$$

$$F_2(A, B, C) = \Sigma m(0, 5, 6, 7)$$

(ii) A 6-bit dual slope ADC uses a reference of 12 V and a fixed count of 010110. Convert the maximum input voltage accurately in digital form.

[15 + 5 marks]

# MADE ERSY Question Cum Answer Booklet Page 21 of 61

Do not write in this margin

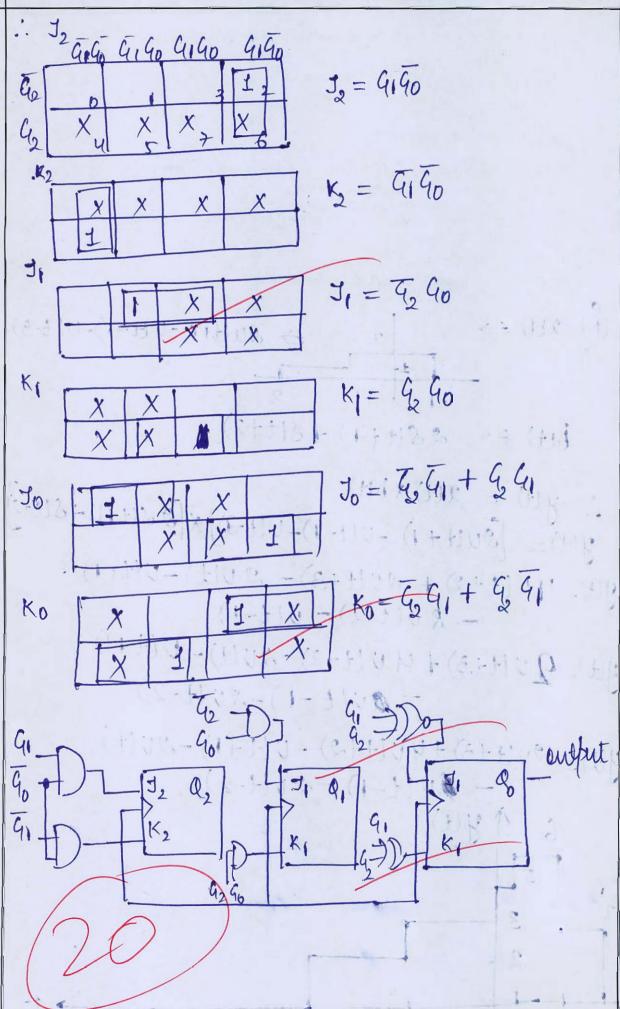

Q.3 (c)

Consider the sequential circuit given below:

- (i) Find the count sequence of the circuit given above. Assume initial condition of flip-flop to be zero.

- (ii) If clock frequency is 160 kHz. Find the frequencies of  $Q_0$  and  $Q_2$ .

- (iii) Sketch the waveforms of clock,  $Q_0$ ,  $Q_1$ ,  $Q_2$  and  $Q_3$ .

[8+4+8 marks]

Do not

write in

this margin

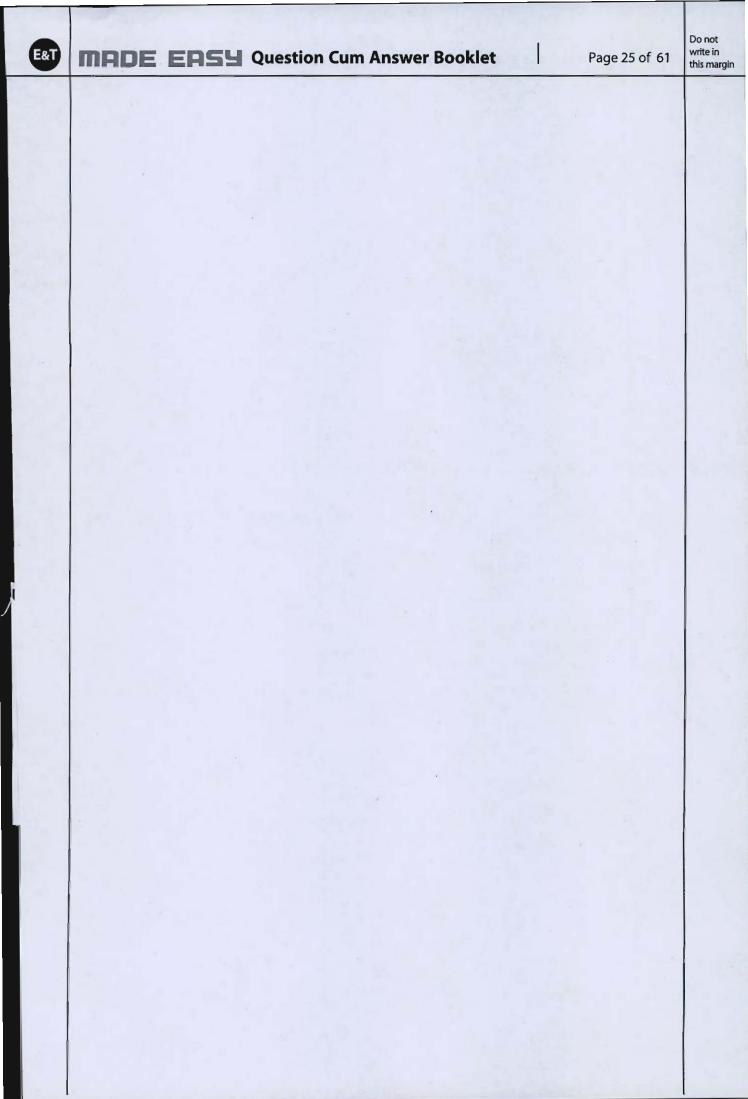

Q.4 (b)

- (i) Implement the logic function  $F(A, B, C, D) = \Sigma m(0, 1, 2, 3, 4, 7, 9, 10)$  using 4:1 MUX only. (Assume only inputs are available)

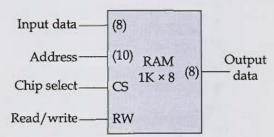

- (ii) Construct a  $4 \text{ K} \times 8 \text{ RAM}$  with  $1 \text{ K} \times 8 \text{ RAM}$  chips. The  $1 \text{ K} \times 8 \text{ RAM}$  is as shown below:

[10 + 10 marks]

### Section B: Digital Circuits + Signals and Systems + Microprocessors & Microcontroller

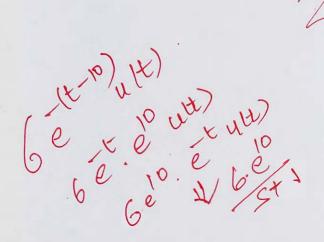

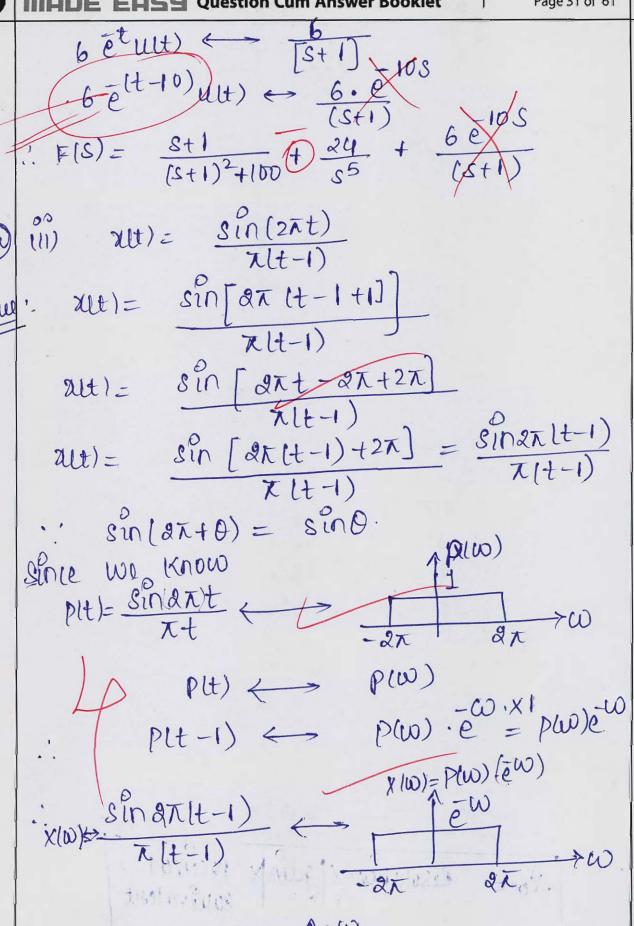

- Q.5 (a) (i) Find the Laplace transform of the function  $f(t) = 2e^{-t}\cos 10t - t^4 + 6e^{-(t-10)}$  for t > 0

- (ii) Find the Fourier transform for the following signal:

$$x(t) = \frac{\sin(2\pi t)}{\pi(t-1)}$$

$$\frac{3000}{(1)} = \frac{3000}{\pi(t-1)}$$

$$\frac{3000}{(1)} = \frac{3000}{\pi(t-1)}$$

$$\frac{1}{(1)} = \frac{300}{\pi(t-1)}$$

$$\frac{1}{(1)} = \frac{3000}{\pi(t-1)}$$

$\chi(\omega) =$

Do not write in

this margin

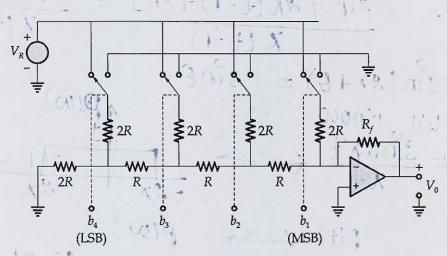

Q.5 (b)

Consider the R-2R, 4-bit converter shown below,

Assume the feedback resistance  $R_f$  of the op-amp is variable, the resistance  $R=5~\mathrm{k}\Omega$  and  $V_R = 10 \text{ V}$ . Determine the value of  $R_f$  that should be connected to achieve the following output conditions:

- The value of 1 LSB at the output is 1 V.

- (ii) An analog output of 8 V for a binary input of 1000.

- (iii) The actual maximum output voltage of 10 V.

Resolution X [12 marks]

2 % 3 ( ) X

(i)

$$R = \frac{v_R}{2^{N-1}} = \frac{10}{2^{N-1}} = 0.666$$

$$I = 0.666 \times \frac{RF}{5 \times 10^3} \times 4.50 \times 10^{-3}$$

$$\therefore RF = \frac{5 \times 10^3}{0.666} \times 4.50 \times 10^{-3}$$

Q.5 (c)

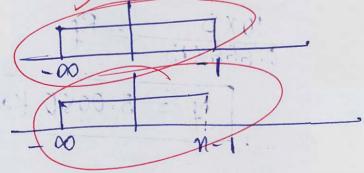

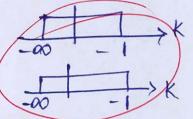

Compute and plot the convolution y[n] = x[n] \* h[n] using time domain approach

sow:

where

$$x[n] = \left(\frac{1}{2}\right)^{(-n-1)} u[-n-1]$$

and  $h[n] = u[n-1]$ .

$$2(n) = \left(\frac{1}{2}\right)^{(-n-1)} u[-n-1] \text{ if } h(n) = u[n-1]$$

$$u[-n-1] \text{ if } h(n) = u[n-1]$$

$$y(n) = \sum_{k=-\infty}^{\infty} x(k) h(n-k)$$

$$|X| = \sum_{k=-\infty}^{\infty} \left(\frac{1}{2}\right)^{(+K-1)} U(-K-1) \cdot U[N-K-1]$$

of

$$\frac{1}{k} = -\infty$$

(1)  $\frac{1}{2}$   $\frac{$

$$y(n) = 2 \sum_{k=-\infty}^{\infty} [(\frac{1}{2})^{+1}]^{k} v(-k-1) v(-k+n-1)$$

$$y(n) = 2 \sum_{k=-\infty}^{\infty} 2^{k} v(-k-1) v(-k+n-1)$$

$$(V - K + N - 1)$$

$\Rightarrow$   $-K + N + 1 = 0$   $(-\infty) < K < N - 1$

Now let us assume three eardinans inc.

708 n=0

-00 KK 4-1

for n=1>0

-00 KK <-1

for n-140  $\gamma < 1$

All are signals. -00 < K <-

for three cases timit of ook<-1 is same.

7(n) = 2 = 2K

- + 2 + 2 T y(n)= 2 [ = 00+

$y(n) = 2 \left[ \frac{\alpha}{3-1} \right] = \frac{2(2^{-1})}{[2^{-1}]}$

y(n)=  $\frac{2 \times \frac{1}{2}}{\left[\frac{1}{2} - 1\right]} = -2$

It will a cknowledge the interrupt and all the data buses are transported for servicing the interrupt.

Q.5 (e)

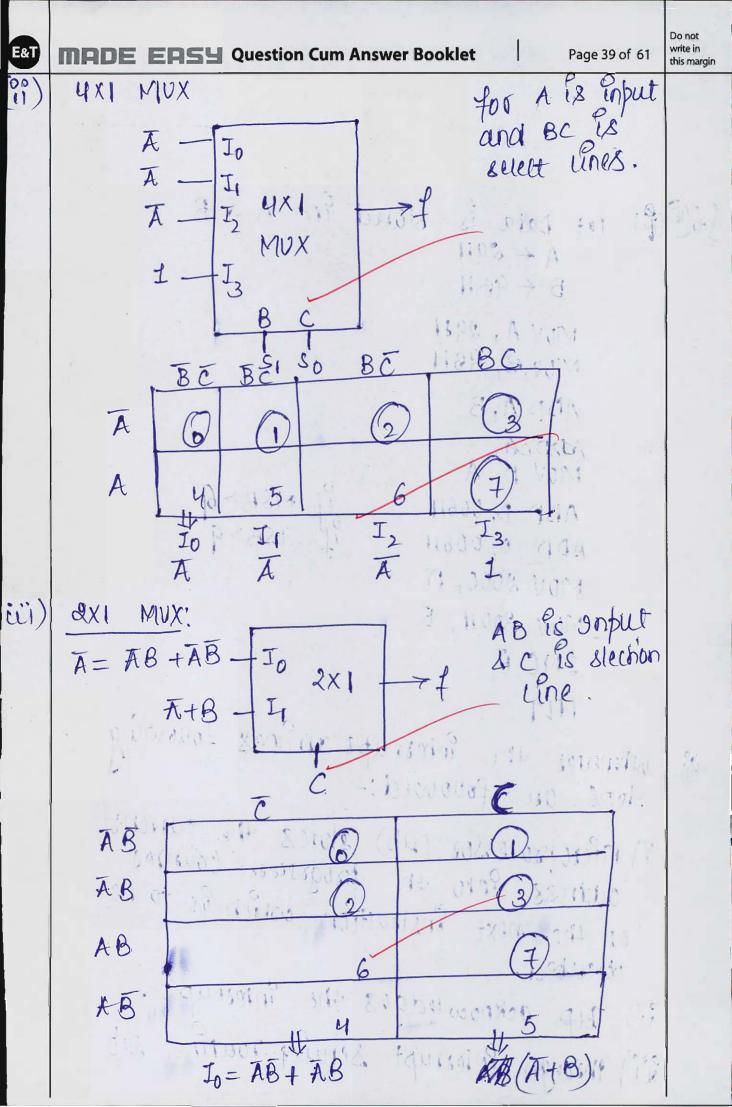

Consider a three input Boolean function  $f(a, b, c) = \sum m(0, 1, 2, 3, 7)$

- (i) Implement the function using a minimal network of 2 × 4 decoder and OR gates.

- (ii) Implement the function using a minimal network of 4 × 1 multiplexers.

- (iii) Implement the function using a minimal network of  $2 \times 1$  multiplexers.

Join.

Do not write in

this man

- Q.6 (b)

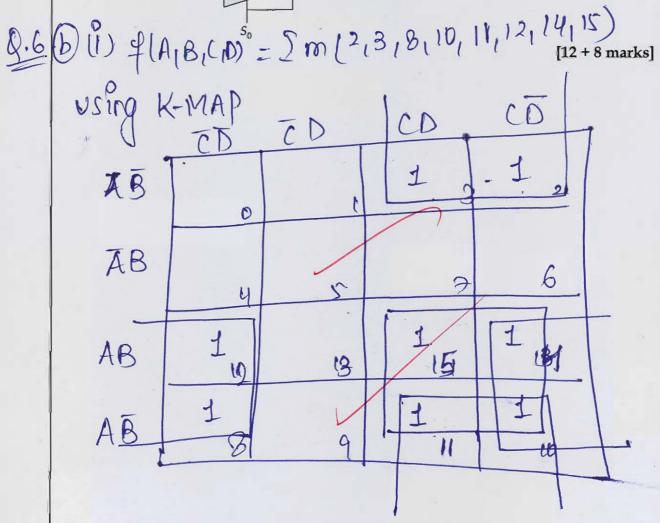

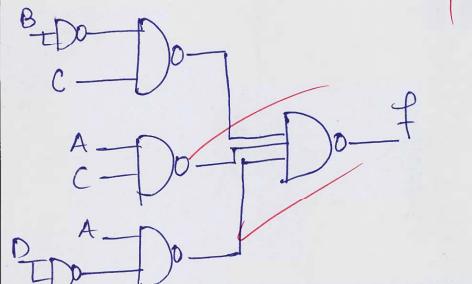

- Minimize the SOP terms given for a Boolean function, (i)  $f(A, B, C, D) = \Sigma m(2, 3, 8, 10, 11, 12, 14, 15)$ Implement the minimized function using NAND gates alone.

- Determine the logic equation for the output by constructing the truth table for the logic circuit shown in figure below:

$$\frac{7 - BC + AC + AD}{\overline{F} = BC + AC + AD} = \overline{BC \cdot AC \cdot AD}$$

(ii)

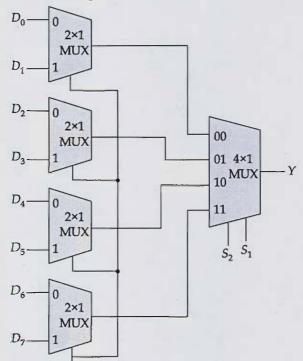

$$y = \overline{3}_{2} \overline{S}_{1} A + S_{2} S_{1} B + S_{2} S_{1} C + S_{2} S_{1} D$$

where,

$$A = \overline{S_0} \cdot B_0 + S_0 \cdot D_1$$

6 (c)

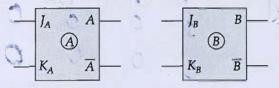

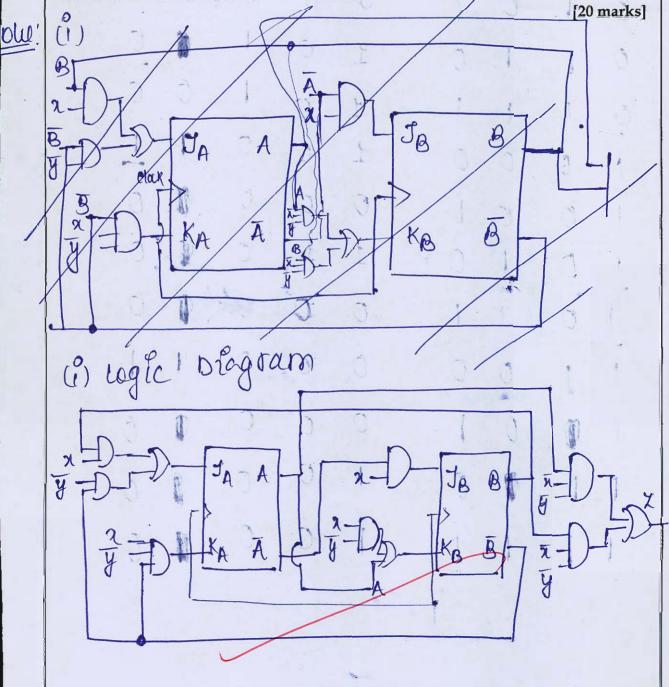

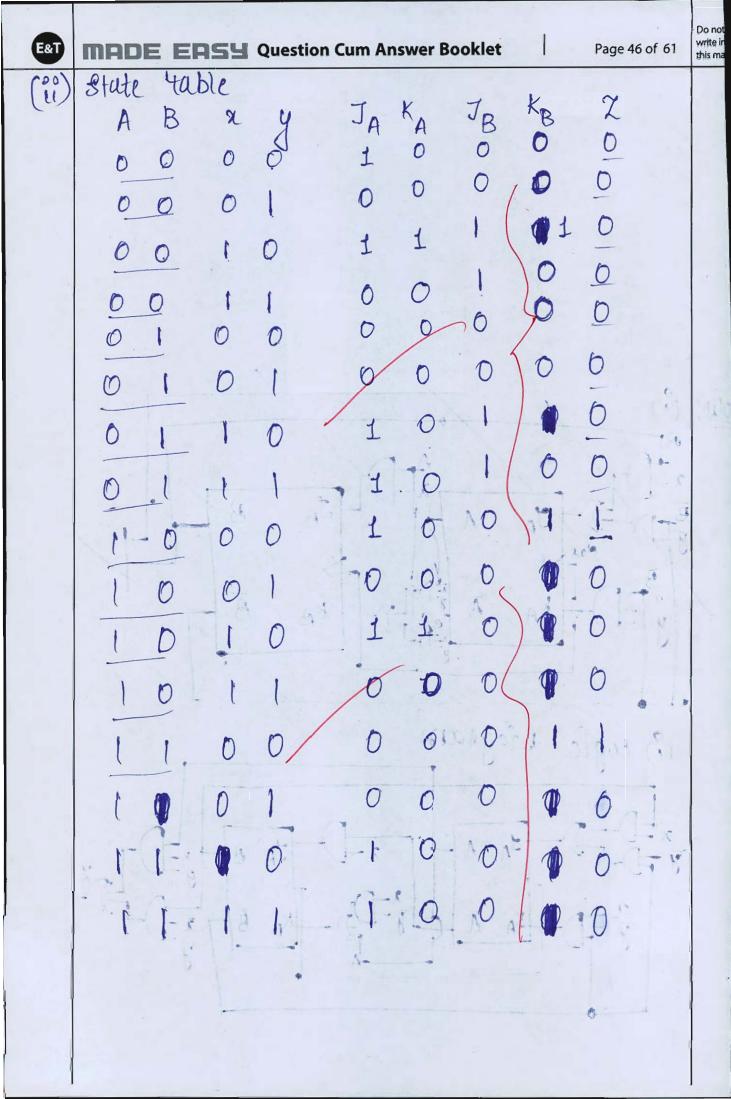

A sequential circuit has two J-K flip flops A and B as shown below, two inputs x and y, and one output Z. The flip flop input equations and circuit output equation are

$$J_A = Bx + \overline{B}\overline{y};$$

$$K_A = \overline{B} x \overline{y}$$

$$J_B=\bar{A}x;$$

$$K_B = A + x\overline{y}$$

$$Z = A \overline{x} \overline{y} + B \overline{x} \overline{y}$$

- (i) Draw the logic diagram of the circuit.

- (ii) Tabulate the state table.

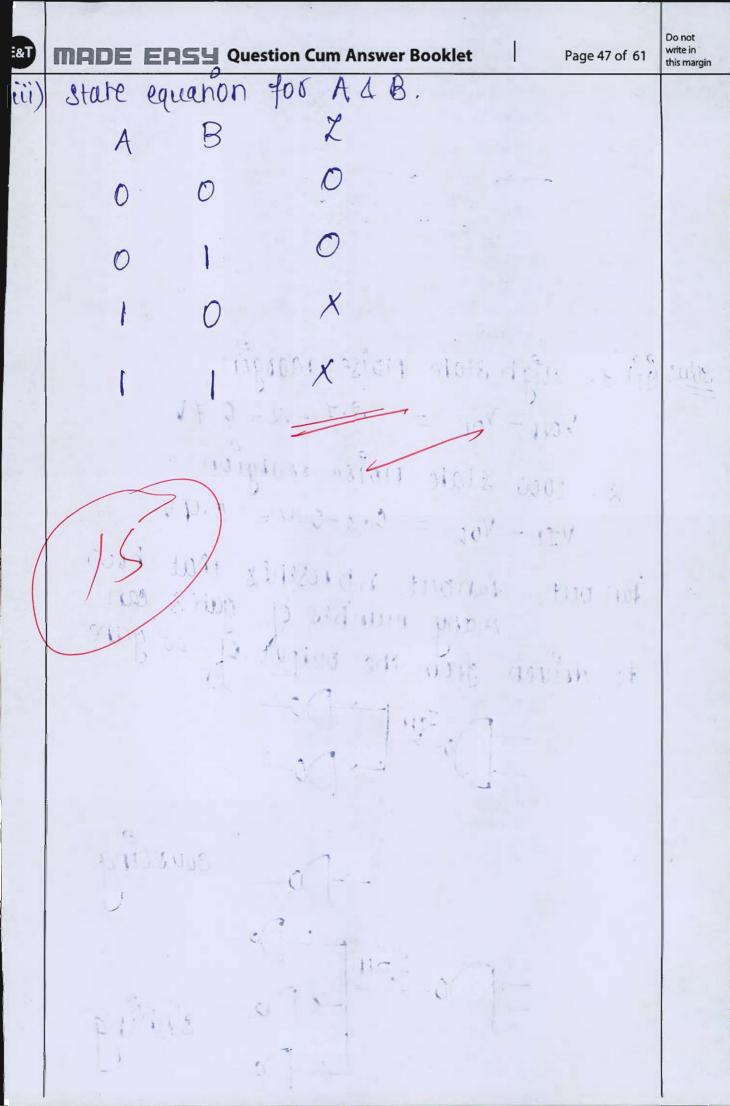

- (iii) Derive the state equations for A and B.

- Q.7 (a)

- (i) With a neat block diagram, explain the operation of counter type ADC. Give advantages and disadvantages of counter type ADC.

- (ii) Define fan-out of a gate. A two-input NAND gate specifications are given as  $I_{OH(\max)} = 0.4 \text{ mA}, \ V_{OH(\min)} = 2.7 \text{ V}, \ V_{IH(\min)} = 2 \text{ V}, \\ V_{IL(\max)} = 0.8 \text{ V}, \ V_{OL(\max)} = 0.4 \text{ V}, I_{OL(\max)} = 8 \text{ mA}, \\ I_{IL(\max)} = 0.4 \text{ mA}, I_{IH(\max)} = 25 \text{ \muA}, \ t_{PLH} = t_{PHL} = 15 \text{ nsec} \\ \text{and supply voltage of 5 V. Determine}$

- 1. High state noise margin.

- 2. Low state noise margin.

- 3. Number of NAND gate inputs that can be driven from the output of a NAND gate of this type.

Solu!

Von - Vol = 2.7 -2 = 0.7V

2. 1000 state moise margion

VIL - VOL = 0.8-0,4=0.4V

fun out: fan out represents that how many number of gares ean be driven from the output of a gare.

Do sous cing

Do I OH Do - sinking

fanout

$$|op = \frac{IoH}{IoL} = \frac{0.4}{8} = 0.05$$

fanout|

$$sip = \frac{TIL}{ToL} = \frac{0.4}{25} = 0.016$$

favout =

$$min (0.05, 0.016) = 0.016$$

Sixe for you by a property of the party of t

(31) - (201) (3)

Structor

J = 04 - 6 - 5

(83.4) = (86) AUT (104) (80) (61)

Haltagard

Q.7(b)

Each of the following arithmetic operation is correct in atleast one number system. Determine the possible bases in each operation.

(i)

$$3441 + 4235 = 7676$$

(ii)  $\frac{142}{7} = 16$

(iii)

$$23 + 44 + 14 + 32 = 223$$

(iv)  $21 \times 16 = 366$

(v)

$$\frac{302}{20} = 12.1$$

(vi)  $\sqrt{51} = 6$

$$\frac{3941}{20} = (1) (3441) + (4235) = (1676) = (1676) = (14835) = (1676) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = (14835) = ($$

$$3\times10+9\times10^{1}+5\times10^{0}=(7676)_{10}$$

Hence, base of number system is 10.

$$(11)$$

$(142)_{2} = (16)_{2}$

$$\frac{x^2 + 4x + 2}{7} = x + 6$$

$$2^{2} + 4x + 2 = 4x + 42$$

$$\eta^2 - 3\chi - 40 = 0$$

on solving x=8.80 base is 8.

22+3+42+4+2+4+3x+2= 2x2+2a+3

$$10x + 13 = 2x^2 + 2x + 3$$

$$2x^{2}+2x-10x-13+3=0$$

$2x^{2}+2x-10=0$  on soluting

$x^{2}-4x-5=0$   $x=5$

$$\chi^2 - 4\chi - 5 = 0$$

2.7(c)

$(81)_{x}(6)_{x} = (366)_{x}$  $\left[2x+\chi^2\right]\times\left[\chi+6\right]=3\chi^2+6\chi+6$  $2x^{2}+13x+6=3x^{2}+6x+6$   $x^{2}-7x=0$   $x(x-7)=0 \Rightarrow x=0$ = (2.1) x  $\frac{3x^2+2}{2x} = x+2x+x' \Rightarrow 3x^2+2 = 2x^2+4x+2xx$ Not = 6 on whole squaring & solleing (51) = (6x6) x said of the system is 7:6+6=12 841/2 34x61 31

Consider a discrete-time low-pass filter whose impulse response h[n] is known to be (i) real and whose frequency response magnitude in the region –  $\pi \le \omega \le \pi$  is given as,

$$\left| H\left(e^{jw}\right) \right| = \begin{cases} 1; & |\omega| \le \frac{\pi}{3} \\ 0; & \text{otherwise} \end{cases}$$

Determine the real-valued impulse response h[n] for this filter when the corresponding group-delay function is  $\tau_{g}(\omega) = \frac{3}{2}$ .

Design a block level architecture of a 5 coefficient FIR filter by using appropriate number of multipliers, adders and registers. Assume that all the input operands are available in 4 bit, 2's complement fixed point representation. The architecture should give one output per clock cycle.

[10 + 10 marks] G(w) is the group delay of the system

$$cg = -\frac{d\phi(co)}{dco}$$

(g(w)= 3

- Q.8 (a)

- (i) Draw the block diagram of programmable peripheral interface 8255A.

- (ii) Explain BSR (Bit Set/Reset) mode of 8255A

- (iii) Write a BSR control word subroutine to set bits PC<sub>7</sub> and PC<sub>3</sub> and reset them after some delay, using the below I/O port addresses.

| Cs             |   |   |       |   |       |       |                  | Hexadecimal<br>Address | Port             |

|----------------|---|---|-------|---|-------|-------|------------------|------------------------|------------------|

| A <sub>7</sub> |   |   | $A_4$ |   | $A_2$ | $A_1$ | A <sub>0</sub> 0 | = 80H                  | A                |

| 1              | 0 | 0 | 0     | 0 | 0     | 0     | 1                | = 81H                  | В                |

| 1              | 0 | 0 | 0     | 0 | 0     | 1     | 0                | = 82H                  | С                |

| 1              | 0 | 0 | 0     | 0 | 0     | 1     | 1                | = 83H                  | Control Register |

[20 marks]

B (b)

(i) Suppose we are given the following information about a continuous time periodic signal x(t) with period 3 and Fourier series coefficients  $a_k$ :

$$1. \quad a_k = a_{k+2}$$

2.

$$a_k = a_{-k}$$

$$3. \quad \int\limits_{-0.5}^{0.5} x(t)dt = 1$$

4.

$$\int_{0.5}^{1.5} x(t)dt = 2$$

Determine x(t).

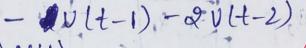

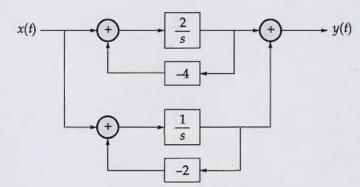

(ii) A causal LTI system 'S' has the block diagram representation as shown in figure below.

Determine a differential equation relating the input x(t) to the output y(t) of this system.

[10 + 10 marks]

Q.8 (c)

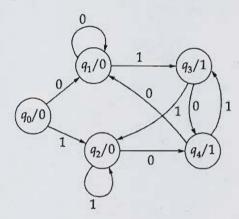

Consider the state diagram of Moore machine shown below:

Get the excitation equations and Boolean equations for output Z of Mealy machine. Also design the Mealy machine using J-K flip-flop.

[20 marks]

Space for Rough Work 122+1)(2+6) 22+122+246 151 A 0,1,2,3 ult) = { 22-3x-40=0 UX1 mut & The F1 = 6 (51)=6 0006 t-hot esto. gin 27(t-1+1) (51)=(6)x(6)x6. 241/48/4. 10) (S-11-0) 6+6=12 x14-1 sin[ant on + 27) x(t-1) sin [an(t-1) + 2h] (S-1) &+ 2) 80 360+0'= 8100. 51/5-Vo=PXONA 10(9) 5-1 5-1 [2] 2 5 f f f 5 f f f 5 f f f 6000 18 fff 5 Ty(++2-1) 1-(AB)(A+B)5-1 FIBT AB FAB v(t-3) v(t-3) v(t-3/3) v(t+1-3)